IEEE授予台积电7nm领先奖。台积电的下一步是什么?

12月17日,2020年经过卢克詹姆斯TSMC已被IEEE正式认可,其中2021年IEEE公司创新奖。但是,7nm节点只是台积电计划的开头。

TSMC已经授予其在7纳米半导体铸造技术中的领导力,一个能够从电子产品制造商广泛创新的节点都大而小。IEEE的企业创新奖是为公司,政府和学术组织保留的,这些组织在IEEE的利益领域中表现出了杰出的创新。

2021年企业创新奖具体揭示了台积电的技术领导层与其开放式创新平台,这两者都为5G移动和高性能计算的新产品铺平了道路。

7nm领导

“台积电在开发7nm技术和促进世界各地集成电路设计器创新方面的成就,使其成为一批对工程领域和世界做出持久贡献的组织之一,”IEEE总裁Toshio Fukuda说。

2016年,台积电的7nm FinFET技术交付使用256MB SRAM.。使用的图像礼貌台长

台积电的业务方法及其铸造模型意味着其7nm工艺技术是世界上最先进的逻辑技术首次可供整个半导体行业作为开放式平台。

自2018年4月进入批量生产以来,TSMC为数十个客户的数百种产品制造了超过10亿美元的模具,在数据中心,5G,高性能计算和人工智能等领域启用创新。

“我们感谢IEEE授予我们这一享有盛誉的荣誉;这给了我们进一步的灵感,让我们继续寻找新的方式来释放客户的创新。”台积电董事长刘益谦表示。

超过7nm

7NM不是近年来台积电卓越的技术。

早在2019年初,这家台湾公司就破例成为首家将完整的5纳米制程技术设计基础设施推向市场的芯片制造商。到年底,TSMC已经排队了顾客的5nm流程,宣布它将成为一个选择的Asics,现在已知的少数内容包括Apple,Intel,Mediatek,Nvidia和Qualcomm。

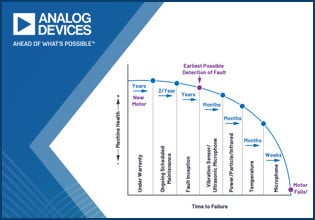

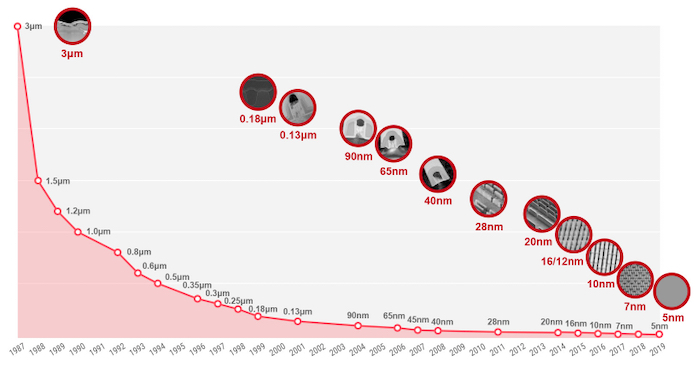

TSMC的铸造工艺技术可以在上述时间线上看到,1987年在3微米后休息,其第一工艺技术在内部开发。使用的图像礼貌台长

与台积电5 nm节点除了逻辑密度比7nm增加1.84倍之外,还将在功率、性能和尺寸方面带来一系列改进。该工艺技术为移动和高性能计算而设计和优化,是台积电第二种利用极紫外(EUV)光刻技术的工艺。

它还提供最高的晶体管密度迄今为止,将激烈应用所需的所有电力包装成它们所需的较小占用空间和功耗水平。

下次TSMC是什么?

尽管7nm仍然是一个新的过程技术,并且在10月中旬的5nm节点上商业化的第一个设备,TSMC已经展望了3nm和2nm。

在台积电的年度技术研讨会上(今年在线进行),台湾半导体巨头的详细特征其未来的3nm制程节点自2019年后期以来一直在努力工作。

该公司上个月最终确定了其195亿美元的39亿美元的建设。根据台积电,3nm制程必将成为世界上最快、最先进的逻辑技术到目前为止,性能提升和功率降低分别高达15%和30%,逻辑密度增益70%超过5nm。

至于2nm,台积电还没有透露太多,评论员预计TSMC将在2023或2024年开始出现风险生产,但这不是石头。至于可能超过2nm,TSMC尚未宣布或暗示任何内容。

不过,英特尔的its2019到2029路线图。英特尔预计将在2023、2025、2027和2029年推出“基本的新节点”,最终将推出1.4nm。考虑到英特尔与7nm的问题在美国,这一路线图遭到了一些质疑。