通过仿真了解并缓解电机驱动板寄生现象

2月4日,2021年通过Matt Hein,德克萨斯州仪器本文探讨了TI的PSPICbeplay体育下载不了E,以模拟电动驱动设计中寄生效应的潜在原因,并提供设计提示,以减轻高功率电机驱动系统的负面影响。

大功率系统设计中最令人沮丧的部分之一是寄生效应的常见效果。这尤其适用于大型板设计,大型部件和高输出电流的高功率电动驱动系统,可以导致输出振铃,过度分量等级或辐射电磁干扰(EMI)。在本文中,我会使用PSpice®为TI模拟电动驱动设计中寄生效应的潜在原因,并提供设计提示,以减轻负面影响。

什么是高功率电机驱动设计?

作为一个完全沉浸在电机驱动系统中的人,我经常认为根据特定的挑战如何构建电机驱动系统的基础知识是理所当然的。寄生分析在大功率系统中变得至关重要有两个很好的原因。

首先,具有高功率的高电流:在电动机中的切换1a在电动机中的开关100a具有相同的效果。具有高电流,印刷电路板(PCB)上固有的所有这些寄生电感和电容跳出并开始造成麻烦。较低的你可以保持当前的,这些寄生成分越少。然而,对于具有定义的高输出功率的系统,目标输出电流是固定的 - 用任何杂散电感和电容设定在碰撞过程中的设计。

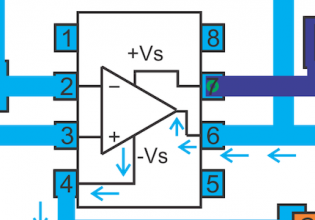

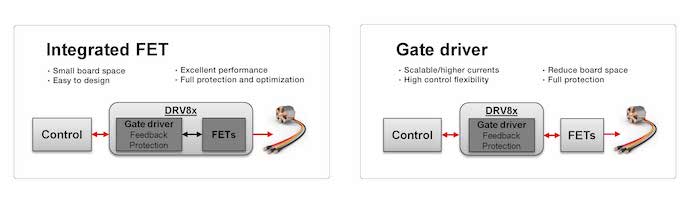

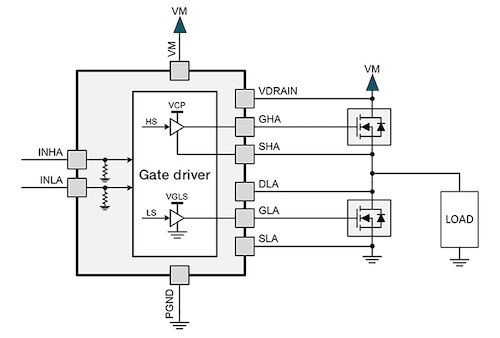

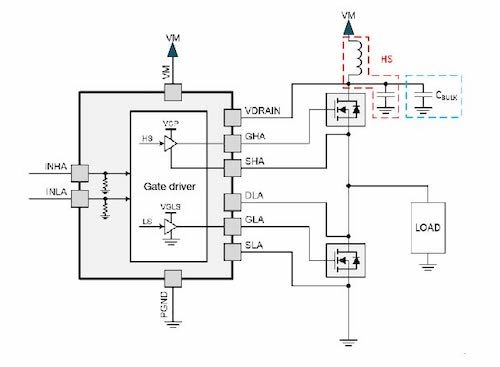

其次,高功率电机驱动系统需要栅极驱动器架构。电机驱动器有两种口味:集成FET(场效应晶体管)和带外部FET的栅极驱动器 - 见图1.集成FET电机驱动器对低功率系统非常有效,因为它们集成了栅极驱动器,功率级和任何其他传感和保护成一个包装。这些设备也令人难以置信 - 例如,DRV8837C只有2x2 mm,因此它们显著减少了板寄生。

不幸的是,即使是最高电流的集成FET解决方案(例如DRV8873-Q1能够驱动高达10a),因此需要网关驱动架构。当在电机驱动系统中使用栅极驱动和外部离散mosfet时,电路板上的元件之间总会有一些PCB迹线,这有助于寄生效应。

图1所示。集成场效应晶体管与栅极驱动架构

栅极驱动电路和应用脉冲

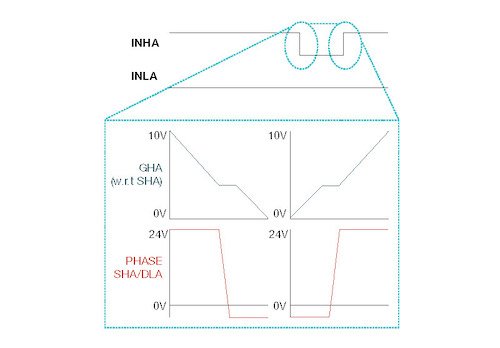

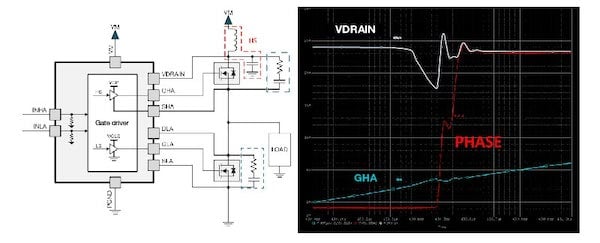

为了构建一个用于分析的电路,让我们从一个简化的半桥电机驱动器开始(图2)。我在这个电路中使用的电机驱动器是Texas Instruments (TI)DRV8343-Q1,三相智能栅极电机驱动器,具有电流分流放大器。mosfet是ti的CSD18540Q5B而我选择的栅极驱动强度(IDRIVE)是15ma源和30ma sink。为了简单,我只使用了一个阶段并创建了一个模型负载(240 m ω和50µH)。这种情况下使用的电源是24v。

图2。简化驱动电路(无寄生元件)

接下来,我模拟了一个“脉冲测试”,涉及在高侧MOSFET上打开一定时间,然后在显着电流流过电路时快速脉冲它。模拟脉冲测试将使您可以观察输出的下降和上升沿所产生的任何效果,因为高侧MOSFET关闭并重新打开。

在图3中,你可以看到应用的控制信号,期望的理想波形的高侧门和输出电压。在这个模拟中,高侧MOSFET被打开为400µs,低脉冲为30µs,并在剩下的70µs带来高。低侧MOSFET保持关闭状态,因此任何电流通过低侧MOSFET体二极管传导。

图3。脉冲测试波形(无寄生元件)

添加寄生组件和模拟

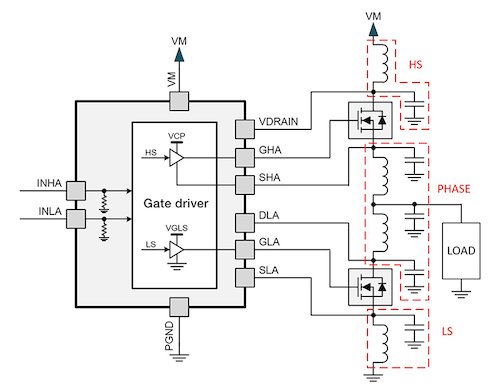

如果在该电路中添加预期的寄生成分,复杂性相当快地增加;电路原理图不再看起来“很好”。为此,您需要在三个地方添加重要的寄生组件:

- 在电源和高侧MOSFET (HS)之间。

- 在地和低侧MOSFET (LS)之间。

- 在高端和低侧MOSFET(相位)之间。

这三个位置是您通常会在PCB上看到明显大的迹线,对应于携带高电流的网。看看图4。

图4。寄生元件驱动电路

对于寄生值,我使用以下内容:

- 高侧(HS):10 NF,5 NH / 10MΩ。

- 相位(相位):2 nF, 2 nH/2 m ω(每路径,附加10 nF输出到负载)。

- 低侧(LS):10 NF,5 NH / 10MΩ。

因为这只是一个模拟,所以我使用了(潜在的)夸张的寄生电感和电容。可以设计一种板子,使这些寄生组件最小化,从而使缓解更容易(尽管遵循相同的过程)。相反,一个设计不好的PCB可能会有更多的寄生电感和电容,这会使减轻寄生效应变得更加困难。为了回顾汽车驱动器的布局技术,我推荐电机驱动程序董事会布局的最佳实践应用程序的注意。

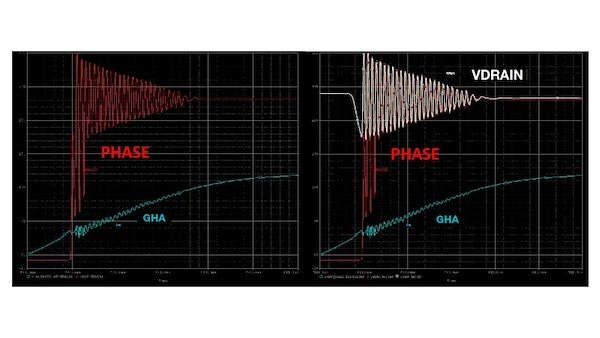

当我之前模拟电路(图2)和之后(图4)添加了这些寄生组件,我得到了我折断了电路的压倒性。查看图5,在开关高或低时,在相位上看到显着的振荡。重要的是要减轻这些效果,以保护电路免受损坏(例如-20-V负电压尖峰)或防止任何不需要的电磁辐射(振荡网将充当天线)。

图5。PSpice对添加寄生元件前后的TI模拟结果

为了找出最佳的缓解行动,让我们逐个分解不同的寄生组件,并模拟每个组件的影响。

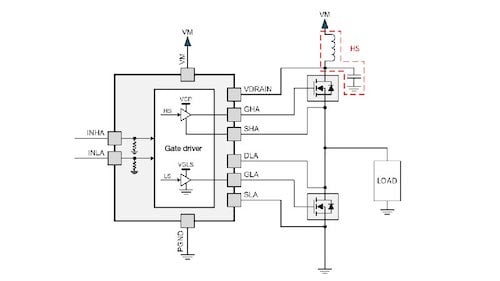

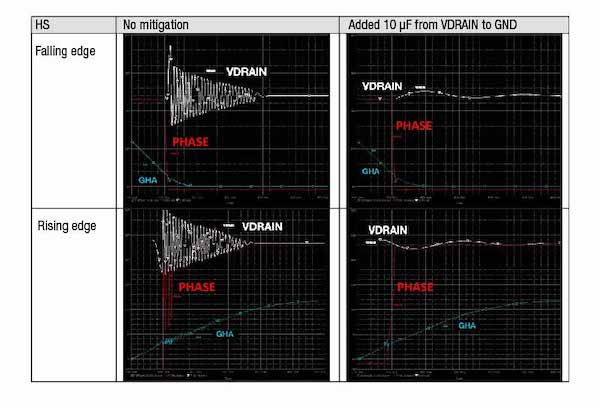

电源和高侧MOSFET之间的寄生元件(HS)

当我在电源和高端MOSFET之间添加寄生分量(图6)时,模拟在上升沿的输出上显示了非常明显的振荡(图7)。挖掘更详细信息,您可以看到振荡来自高端MOSFET(VDRAIN)的漏极。在下降沿,当高端MOSFET关闭时,即使输出不受影响,您也会看到相同的效果。

图6。高侧路径寄生驱动电路(HS)

图7。增加寄生在高边路径(HS)上的上升边缘模拟

在这个阶段,您可能认为需要添加缓冲器,或者转换速率太高,需要减少。考虑一下:缓冲器将在减少阶段振荡时最有效,而不是Vdrain振荡。对于调查,我在高端和低端MOSFET上实施了一个1.2Ω和33 NF的缓冲器。您可以看到图8中的效果,其中Vdrain仍会在切换事件之前删除,因此这不是减轻振动的最佳方法。

图8。尽管有缓冲,但由于VDRAIN上的振荡,减缓并不有效

要了解更多关于缓冲器设计的信息,请查看技术文章能量提示:计算一个R-C缓冲器有七个步骤。

减少振荡的另一种可能的解决方案是降低旋转速率,在模拟中,这将显著减少但不能消除振铃现象(图9)。由于更高的开关损耗,降低的旋转速率会导致更多的功率损耗(更热的部件),应该尽可能避免。在这个例子中,我将栅极驱动电流从15毫安源降低到1.5毫安源-增加了10倍的上升时间。

图9。尽管闸门驱动电流降低和更长的上升时间,但由于较高的功耗和振荡,减轻不效是无效的

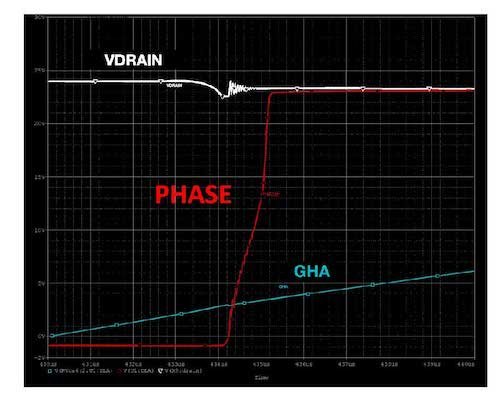

为了更好地缓解这些效果,让我们在VDRain节点上添加一个大的散装电容(图10);这将使振荡显着较慢,幅度较小。我简单地使这个电感电容器时间恒定,更长。图11显示了这种添加的结果。

在模拟中,增加了体积电容,使峰值振荡从37v(电源上方13v)降低到更容易控制的25v(电源上方1v)。该电容必须放置在靠近高侧MOSFET尽可能减少任何额外的寄生电感电容和MOSFET之间。陶瓷电容器因其较低的引线电感和较好的高频响应而更可取。

图10。在VDRAIN上添加散装电容

图11。采用大容量电容(VDRAIN到GND)缓解高侧寄生元件

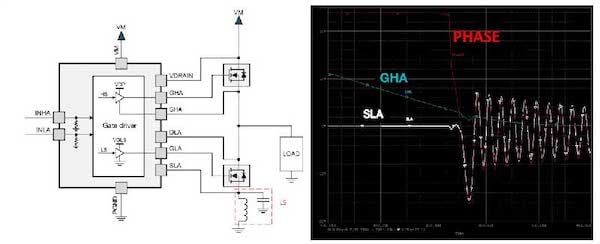

地面和低端MOSFET(LS)之间的寄生组件

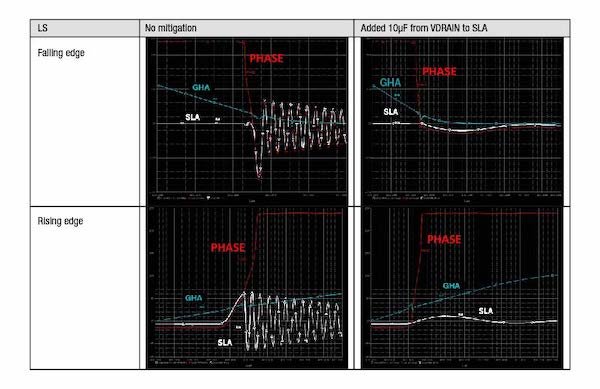

低侧路径几乎与高侧路径相反。下降的边缘导致了显著的振荡,而上升的边缘看起来很干净。仔细观察,你可以看到低侧MOSFET源节点(SLA)在上升边和下降边振铃(图12)。

图12。添加到低端路径(LS)中的寄生菌的示意性和模拟

面对这种情况时,你们中的一些人会想要增加缓冲或延长上升时间来对抗铃声,但是,在这种情况下,你也应该避免这种方法。正如我之前所做的,我在高侧和低侧MOSFET上都实现了1.2 ω和33nf的缓冲。结果是在相位振荡上有了显著的改善,但初始负电压脉冲仍然存在(图13)。

图13。尽管有缓冲,缓解是无效的,因为一个负电压尖峰

如果降低旋转率,振铃将显著减少(图14)。在本例中,栅极驱动电流从30ma汇聚降至7ma汇聚;一个>4倍的下落时间。

图14。尽管闸门驱动电流降低和较长的上升时间,但由于较高的功耗,减缓无效

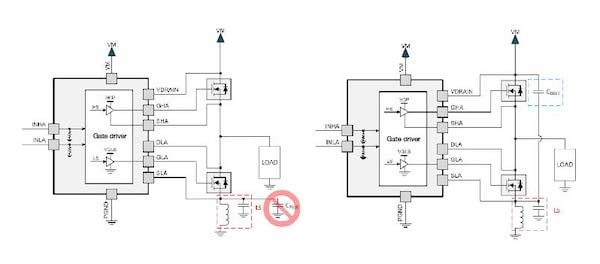

您可以采取类似的方法在高端壳体上,并向电路板添加额外的散装电容以对此振铃进行计数。但是,在这种情况下,您不希望将来自SLA的大电容添加到地。大多数电动机驱动系统使用电流检测电阻和电流检测放大器在低端实施电流检测。典型的2512封装检测电阻将具有1至5 nH的寄生电感,向我们假定的寄生值贷款将一些信用贷款。

与检测电阻平行的一个非常大的电容器将抑制系统正确检测电流的能力(图15)。添加此散装电容的正确位置是从VDRAIN到低端源(SLA)。请记住,当添加该解耦电容时,仍然会对峰值电流产生一些影响。这种电容器的非常大的值将影响通过低侧电流检测的任何峰值过电流限制。

图15。错误(左)和正确的位置(右)的散装电容器减轻低侧寄生

图16演示了这种添加的结果。在仿真中,体积电容的增加显著降低了峰值振荡从- 16v到- 3v。与前面的例子类似,这个电容必须放置在尽可能靠近高侧MOSFET漏极和低侧MOSFET源的地方,以减少电容和MOSFET之间的任何额外寄生电感。由于陶瓷电容器具有较低的引线电感和较好的高频响应,因此仍然是首选。

图16。采用体积电容(VDRAIN to SLA)缓解低侧寄生组件

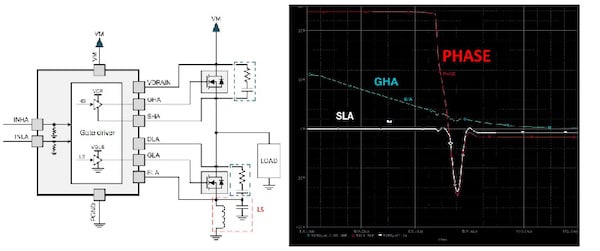

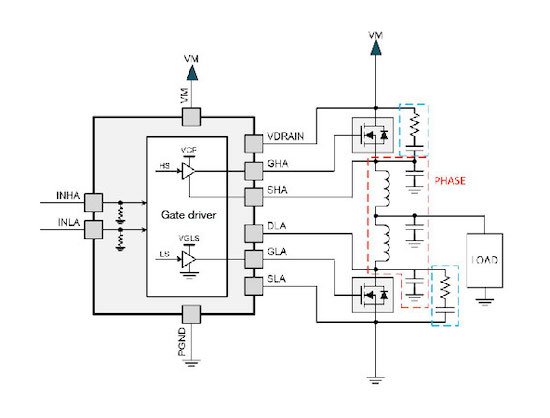

mosfet之间的寄生元件(相位)

你可能已经知道,你应该总是让你的高边和低边mosfet尽可能地靠近,以减少开关时的寄生效应。这是非常好的建议,但你永远不能完全消除这些负面影响。

即使是最有效的多模MOSFET解决方案(参见CSD88599Q5DC例如)在高侧和低侧场效应管之间仍然有一些寄生电感和电容。MOSFET输出电容(COSS)和电机电缆电容(在较长的电缆长度下)对PCB外部相节点上的电容有重要影响。

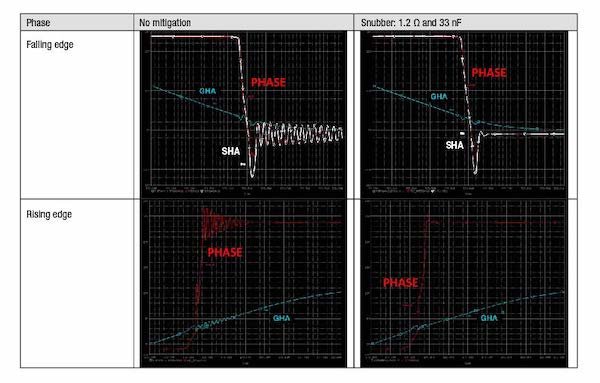

在这种情况下,不可能向电路添加额外的体电容以绕过寄生电感。电机输出将在高低,低电平,此网上的附加大电容器将反复充电和放电 - 一个非常低效的系统解决方案。当发生这种情况时,最好将缓冲器作为第一策略(图17)。

如果你是一个缓冲支持者,你可以呼吸浮雕 - 让我们现在使用它们!您可以看到将缓冲器添加到图18中的电路中的效果。

图17。与寄生添加到相位路径(相位)和额外的缓冲器的示意图

图18。带有缓冲器的缓和相位寄生元件

缓冲器几乎完全解决了上升沿的振荡,并显着提高了下降沿的情况。就像在先前的实验中一样,我在高端和低端MOSFET上实施了1.2Ω和33 NF的缓冲器。然而,与低端MOSFET寄生盒(图14)一样,第一负脉冲保持。

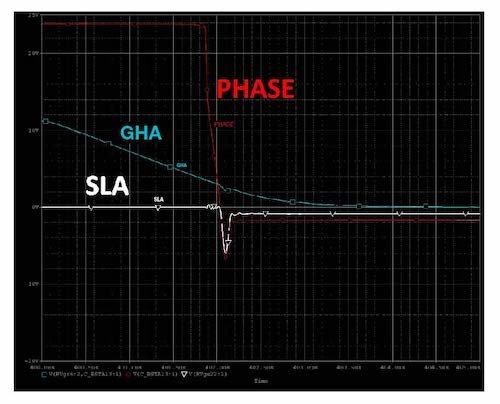

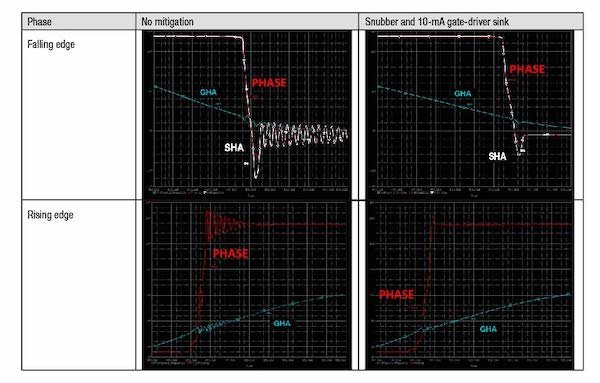

在这个阶段,您可以得出结论,需要增加下降时间,以便完全克服这些寄生效应。您必须在图18中的下降沿上提高-11-V负电压尖峰,以便您保持在绝对最大额定值范围内DRV8343-Q1(200 ns -7 V)。当你将栅极驱动电流吸收从30 mA降低到10 mA时,你会在最大额定范围内得到这个负尖峰(图19)。

图19。具有缓冲器和减小栅驱动电流吸收的缓和相位寄生元件

把它们放在一起

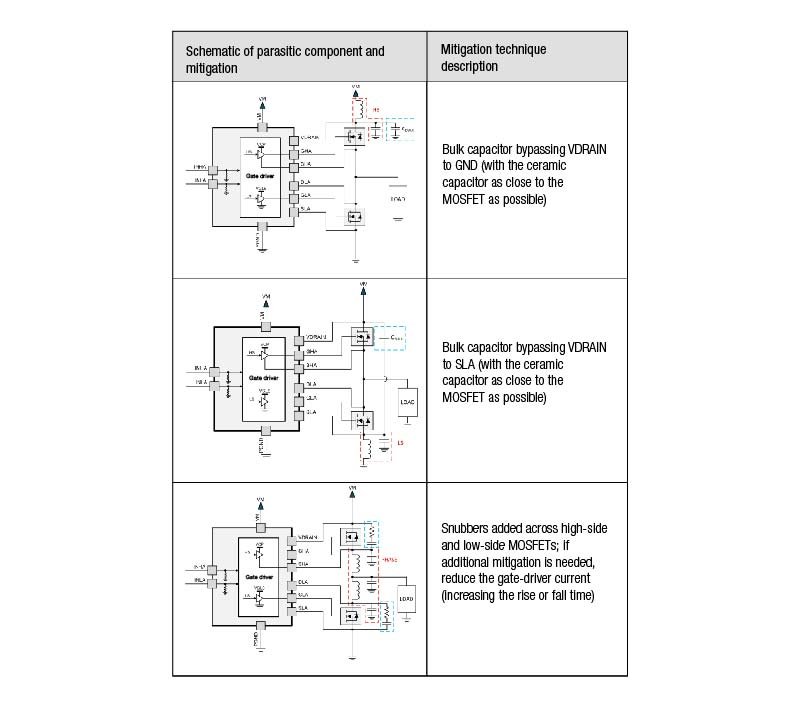

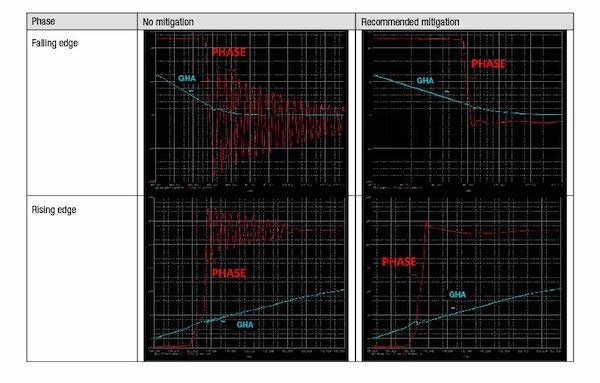

那么通过这个模拟练习我们学到了什么呢?对于这三种常见的寄生效应(高侧、低侧和相位),有三种不同的缓解技术。如果将本文描述的所有缓解技术应用于包含所有寄生元件的电路(表1),就可以显著减少超调、欠调和振铃(图20)。

表1。寄生成分缓解技术综述

图20。使用概述的方法减轻所有寄生成分

这对我来说是一个特别有趣的练习,因为它给了我一个很好的机会来尝试的原理图和模拟功能PSpice为TI仿真工具。这些模拟比物理板实验更容易且更快,并且可以在遇到船用寄生虫的真实问题时,可以提供良好的见解。

如果您想了解有关TI的PSPICE的更多信息,您可以阅读技术文章如何使用PSPICE模拟复杂的模拟电源和信号链电路或者观看视频培训系列PSpice for TI:介绍。有关TI电机驱动因素,培训和资源的更多信息,请访问汽车司机产品网页。

行业文章是一种内容的形式,允许行业合作伙伴分享有用的新闻,消息和技术,所有关于电路读者的行为编辑内容并不适合。所有行业文章都受到严格的编辑准则,目的是提供读者有用的新闻,技术专业知识或故事。在行业文章中表达的观点和意见是合作伙伴的观点,不一定是关于电路或其作家的所有人。