嵌入式微带阻抗计算器

此计算器可帮助您计算嵌入式微带的特征阻抗。

输出

概述

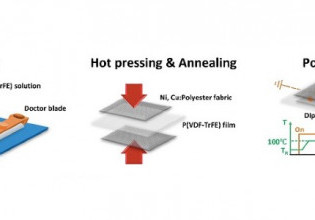

该计算器旨在计算嵌入式微带的特性阻抗 - 悬挂在接地平面上的扁平导体,其电介质与导体上方的另一电介质材料(参见下图)。嵌入式微轨通常使用印刷电路板制成,尽管可以使用其他材料。嵌入式微带可以使用具有焊接掩模的微带的微带构造。

只需在上面的计算器中输入迹线厚度,基板高度,迹线宽度和子电氢电介质的给定值,然后按“计算”按钮。除子外电介质之外,所有给定值的默认单位都是毫米。可以选择其他单位。注意:高度H1的值不能高于高度H2。如果是这种情况,计算器将提供零。

方程式

$$ z_ {0_ {emed}} = z_ {0} \ left \ {\ frac {1} {\ sqrt {e ^ {\ frac {-2b}} + \ frac {er}{z_ {0surf} e_ {reff}}(1-e ^ {\ frac {-2b} {h_ {1}})} \ right \} $$

在哪里:

$$ er_ {eff} = \ frac {er + 1} {2} + \ frac {er-1} {2} \ left \ {\ sqrt {\ frac {w} {w + 12h_ {1}}}}} +0.04(1- \ FRAC {W} {H_ {1})^ 2 \右\} $$何时$$ \ frac {w} {h_ {1}} <1 $$

$$ er_ {eff} = \ frac {er + 1} {2} + \ frac {er-1} {2} \ left \ {\ sqrt {\ frac {} {w + 12h_ {1}}}}}右\} $$何时$$ \ frac {w} {h_ {1}}≥1$$

$$ w_ {eff} = w +左(\ frac {t} {\ pi} \ rote)ln \ left \ {\ frac {4e} {\ sqrt {(\ frac {t} {h})^ 2+(\ frac {t} {w \ pi + 1.1t \ pi})^ 2}} \ \ \ \ frac {e_ {r} +1} {2e_ {r}} $$

$$ x_ {1} = 4(\ frac {14e_ {r} +8} {11e_ {r}})(\ frac {h_ {1}} {w_ {eff}})$$

$$ x_ {2} = \ sqrt {16(\ frac {h_ {1})^ 2(\ frac {14e_ {r} +8} {11e_ {r}})^ 2+(\ frac {e_ {r} +1} {2e_ {r}})\ pi ^ 2} $$

$$ b = h_ {1} - h_ {2} $$

$$ z_ {0_ {嵌入}} $$ =嵌入式微带的特征阻抗以欧姆(ω))。

$$ h_ {1} $$ = Subtrate Heigh 1

$$ h_ {2} $$ = Subtrate高度2

$$ w $$ =跟踪宽度

$$ =跟踪厚度

$$ \ epsilon_ {r} $$ =基板电介质

$$ _ {upf} $$ =有效的基板电介质

资料来源:PC-2141A(2004)“高速控制阻抗电路板的设计指南”

应用程序

除了在导体顶部的附加电介质子流动之外,嵌入式微带具有与微带相似的结构。可以使用嵌入式微带创建微波天线和耦合器以及一些过滤器。这些传输线路不像微轨那么容易制造,但仍远远比传统的波导更便宜,以及更紧凑和更轻。但是,微带不能处理波导可以高达功率水平。微带还具有电力损耗,串扰和无意辐射的问题,因为它们没有像波导一样封闭。

嵌入式微带还在高速数字PCB设计中发现,需要具有最小失真的信号行进,并且不需要串扰和/或辐射。

你好。此页面上列出的等式看起来很有希望,但有任何详细的外观会带来问题:

- 是“H”H1或H2?可能会推测H1和H1排队,但这是假设不确定性

- 是“ER”与介电常数相同?或有效介电常数?

计算器会带来答案,但没有错误检查,或者至少不够。H1可以大于H2,仍然会产生答案。

任何人都可以列出这些方程的原始来源或提供一致的一组吗?

先感谢您。

你好

您可以使用IPC-2141A(2004)勘误表更新此计算器吗?

http://www.ipc.org/4.0_knowledge/4.1_standards/2141a_errate.pdf.

谢谢