西方数字转向开源,使用新的RISC-V核心、ISS和缓存一致性

2018年12月18日,通过凯特·史密斯开源正在改变我们管理数据的方式吗?一年前,数据存储设备公司西部数据(Western Digital)转向了RISC-V的开源指令集架构ISA(指令集架构)。本月,他们宣布了一系列开放源码的合作计划,旨在让数据更加开放,从处理器核心到内存缓存。

开源正在改变我们管理数据的方式吗?一年前,数据存储设备公司西部数据(Western Digital)转向了RISC-V的开源指令集架构ISA(指令集架构)。本月,他们宣布了一系列开放源码的合作计划,旨在让数据更加开放,从处理器核心到内存缓存。

在就职RISC-V在今年12月的峰会上,有许多公告和演讲详细介绍了RISC-V的现状及其对行业的影响——现在和未来。

西部数据(Western Digital)是一家以数据存储设备闻名的公司,也是正在成长中的RISC-V环境中的公司之一。一年前,他们宣布他们将转移到RISC-V。现在,他们正在加倍致力于这种开源架构,旨在促进新的创新,并帮助引领未来的数据处理,最终是数据存储。

在峰会上,西部数字宣布了三条新闻,每一条都与他们在开源领域的工作有关:

- OmniXtend:内存结构

- SweRV核心:自主研发的RISC-V核心

- 一个指令集模拟器

AAC有机会与Western Digital RISC-V生态系统总监Ted Marena进行了交谈,谈论了这些新发展,以及该公司如何处理开源现象。

大数据与快速数据,核心计算与边缘计算

马瑞娜和西部数据在几个方面概括了大数据和快速数据之间的区别。

大数据通常在一个有自己处理流程的核心位置进行处理,并且往往会面临诸如可伸缩性等问题。另一方面,快速数据更适合边缘计算,快速响应非常重要,性能和延迟是主要的挑战。

边缘计算应用程序的一个例子是安全摄像头,其中延迟是一个痛点。系统没有时间将信息发送到云上,而云可以根据数据做出决策——它需要一个更小、更简单的解决方案。

一般的看法是,市场很可能会看到边缘应用的增长趋势,这将需要更多的处理和智能。

为什么开源是未来的趋势

根据marrena的说法,西部数据与RISC-V合作的一个重要原因是,他们发现由于他们的专有接口,通用架构很难使用。早在2014年,该公司就开始相信开放、标准的接口是创新的关键。

这个谜题的另一个部分是始终存在的妖怪——安全。马瑞娜说,总体趋势是,由于在协作环境中有“更多的人”关注情况,开源变得更加安全。

选择开放标准

马瑞娜说,在这个领域还有其他一些由联盟开发的标准(其中一些西方数字也参与其中),其中一些不是开源的。说服一个行业采用开放标准本身就是一个挑战。这样的标准对于大多数现有的架构来说是不可能的。当被问及西方数字如何努力推广开放标准时,Marena解释了该公司在RISC-V峰会上的展台演示。与SiFive合作开发点对点解决方案,与Barefoot网络开发可编程交换机,西部数字展示了他们的新存储结构OmniXtend。

这是一个“实践证明”的案例,西方数字希望通过展示开放标准的实用性和有效性来为其赢得支持。

以下是这些合作的概述——以及西方数字公司对risc - v的关注——已经完成的工作。

OmniXtend:大数据和快速数据的缓存一致性

OmniXtend是一个与缓存一致的“内存结构”,旨在允许在多个不同类型的处理器之间共享访问内存缓存。其理念是,多方(人员或处理器等)将访问相同的内存,从而在系统中实现更好的一致性。

“基本上,我们提出的这种内存结构将允许,比如,一个RISC-V处理器,一个GPU,和一个FPGA共享并以一致的方式访问缓存。这并不一定只是一个RISC-V实现。其他处理器体系结构也可以采用这个标准。这里的变化是,”Marena说,“在今天的架构中,内存到处理器或内存到外设的比例是相当固定和固定的。我们希望做的是让数据成为架构的中心。没有人拥有内存,因此我们认为这可以引入一些真正独特的解决方案。”

“我们希望做的是让数据成为架构的中心。”

Marena帧缓存一致性在处理饥渴的应用程序方面。例如,人工智能需要大量的处理。在这种情况下,大量的AI处理器可以通过网络共享内存。Western Digital认为,这将允许在不久的将来实现特定的应用程序,今天可能需要不同于目前所支持的比率。

“RISC-V允许我们这样做,因为它是开放的,”Marena补充道。“在现有的一些架构下,这种标准是不可能实现的。”

SweRV内核:RISC-V内核

SweRV核心是第一个risc - v设计的核心,将在2019年前几个月以完全开源的形式发布。它是由Western Digital开发的,供内部使用,但后来作为对开源生态系统的贡献而发布。

马丽娜首先打破了“SweRV”这个名字背后的想法:RV是RISC-V的意思,而“我们”则是对项目的协作性质和西方数字的名称的认可。他说,SweRV也是一个动词,表示选择另一条道路,这突显了该公司致力于推动行业变革的决心。

“这正是我们正在做的,”他说。“我们没有使用通用计算。我们希望利用RISC-V为大数据和快速数据提供专门的架构。”

核心本身是一个有序核心,这意味着它一次执行一个指令。

马瑞娜说,这种核心是一种更简单的设计,使其体积更小,耗电更少。他还建议,顺序内核不太容易受到某些安全攻击。

其概念是核心可以作为开发人员创建自己的定制核心的起点,尤其是开源社区。为了方便设计者采用和构建核心的能力,他们还打算提供测试向量。马丽娜说:“我们很高兴看到人们能做些什么。”

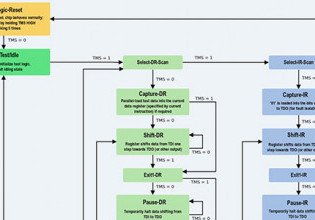

指令集模拟器

最后,西部数字公布了他们的ISS,它允许用户模拟和模拟处理器正在做什么,本质上确保一个设计正在做它应该做的事情。

马丽娜说,国际空间站的“关键一点”是,它是独立于SweRV核心RTL实现的。核心的Verilog RTL是由一个与SweRV ISS完全独立的团队开发的。他们被要求开发一个能够响应RISC-V指令的国际空间站,即使使用的核心是外部的(也就是说,不是来自西方数字)——能够测试他们在软件中输入的任何东西。

“这给人们提供了一个可以进行生产的核心,”Marena说。

未来:RISC-V存储设备

虽然看到一家数据存储设备公司推出核心和模拟器似乎有点奇怪,但它背后有一个更大的计划。马丽娜表示,西部数字计划在2019年底或2020年发布RISC-V数据存储设备。

“这都是关于开放标准接口的,”他说。

你对RISC-V了解多少?您如何看待开源体系结构的这些新趋势?请在下面的评论中分享你的想法。

嘿,凯特!我回来做一些刷新这个网站,因为我正在考虑一个新的商业风险使用我的老comp工程技能。伟大的文章。代我向家人问好!

你好,Kate,在Swerv的ISS模拟器部分,你提到可以使用一个试验台交互。请告诉我你指的是哪种测试平台的详细信息。有可能将SV试验台与ISS集成吗?