到2024年,预计美国数据中心市场将达到超过690亿美元的收入。越来越多的公司和用户依赖于数据中心进行运营和日常使用,具有可靠的硬件和软件对于保持这些服务并运行至关重要。

Micron的DDR5具有两个40位独立通道。使用的图像礼貌微米

实现这一目标的一种主要方法是提高记忆性能 - 某种东西Micron最近宣布其DDR5注册DIMM的抽样(RDIMM)。

DDR5的性能改进

微米DDR5.是第五代双数据速率(DDR)SDRAM。(PDF)DDR5.是DDR4的继承者,并具有显着的改进。

DDR4与DDR5的有效带宽。使用(PDF)的图片微米

在每秒3200兆杯的等效数据速率(MT / S),DDR5的性能增加了1.36倍的有效带宽的性能增加。在更高的数据速率下,4800 MT / s,DDR5性能增加变为DDR4的1.87倍。

这是在快速扩展的数据集和计算密集型应用程序的时候出现了导致处理器核心计数的增长“将通过当前DRAM技术带宽匮乏。”

Micron表示DDR是最新的迄今为止最先进的DRAM,并将通过提供85%的内存性能提高85%来实现下一代服务器工作负载。

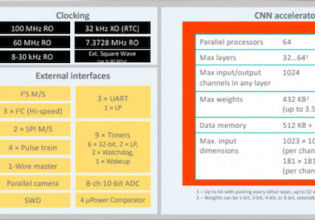

启用数据速率的新功能增加

有许多关键的添加和改进使DDR5的带宽增加。这些包括:

- 占空比调整器(DCA)电路,用于纠正在控制器接收的DQ和DQS信号中发生的小型占空比

- DQS间隔振荡器电路允许控制器由于电压和温度的变化而监测DQS时钟延迟的变化

- 改进的培训模式,包括新的读取前导训练模式,命令和地址训练模式,芯片选择训练模式和写入划平训练模式

- 写入级别允许系统补偿每个DRAM设备和DW和DWS路径的CK路径之间的模块上的定时差异。

- 阅读具有专用模式寄存器的培训模式

- 用于命令和地址引脚,芯片选择引脚和DQ引脚的内部参考电压

可靠性,可用性和可维护性(RAS)

现代数据中心需要可靠性,可用性和可维护性,可通过DDR5的多个功能启用。

在误差校正码(ECC)通过在从DDR5设备输出数据之前,通过在读取命令期间执行校正来减少系统纠错负担。DDR5设计用汉明码实现EDD。

理论DRAM带宽与核心计数趋势。使用的图像礼貌微米

此外,DDR5 SDRAM ECC具有错误检查和擦洗(ECS)函数,该函数是内部数据的读取,如果发生错误,则写回校正数据。ECS可用作手动或自动功能。

包装后修复(PPR)是具有硬(HPPR)和软(SPPR)模式的功能。这两种模式分别对应于永久修复和临时修复。PPR还具有跟踪资源可用性的能力。

在启动时,每个DRAM设备确定每个存储体中PPR资源的可用性,然后设置一组模式寄存器以跟踪信息。

Micron的DDR5 SDRAM产品组合提供了一种功能,旨在为数据中心带来创新和更高的性能。