二硫化钼晶体管可能是微电子学的下一个飞跃

2017年2月13日通过罗宾·米切尔来自斯坦福大学的一组研究人员使用标准的工业生产技术,用二硫化钼制造出了晶体管。一旦用硅不能使晶体管变得更小,硅最终会被取代吗?

来自斯坦福大学的一组研究人员使用标准的工业生产技术,用二硫化钼制造出了晶体管。一旦用硅不能使晶体管变得更小,硅最终会被取代吗?

小问题,大影响

现在已经说了很多次了,在这里还会再说一次——硅正在达到它的极限!由于半导体工业能够减小晶体管的尺寸,工程师们每18个月就能设计出更强大的产品。当一个晶体管的尺寸缩小时,它允许在一个芯片上安装更多的晶体管,这反过来又允许建造更复杂的电路。

一个经典的例子是晶体管数量翻倍对cpu的影响。第一个CPU,英特尔4004,只有2300个晶体管,而下一个CPU, 8008,有3500个晶体管,几乎有两倍的能力(8位比4位,更快的时钟,更大的内存模型)。很明显,晶体管数量的增加使集成电路更好,那么为什么工程师们要担心硅器件的未来发展呢?

英特尔4004帮助地球发生了革命性的变化。图片由Thomas Nguyen提供(CC冲锋队4.0)

最新的晶体管(截至2017年)的尺寸是10nm,这使得晶体管的特征是几十个原子大小的数量级。这样的小型设备越来越难生产,因为要制造这样的特征尺寸需要更先进的设备,而这是有成本的。

但小晶体管的问题不会在那里结束。当晶体管栅极变得非常小(横跨原子)时,量子效应 - 通常微不足道,例如电子隧道变得明显,并且可以具有不利影响。

例如:如果栅极变得太薄,并且电子可以隧道隧道隧道丢失,这需要用户替换该丢失的电荷。结果是晶体管,该晶体管消耗更多的电流,从而导致更散热。单个晶体管(即使非常泄漏)的电流损失和温度升高,而且当1亿设备放置在单件硅上时,效果增加并变成了一个严重的问题。但电流不只是从门泄漏;如果两个靠近接近,电流可以从源隧道到漏极,这可能阻碍晶体管控制电流的能力。

进入钼二硫化物

那么设备如何变得更小?许多工程师和研究人员都有许多想法,包括使用金刚石,石墨烯和甚至有机化合物。

最近,斯坦福大学的一个团队创建了一个1nm晶体管使用二硫化钼,但生产困难。这项工作由美国科学院的研究人员进一步推进IEEE国际电子设备会议去年12月,世卫组织使用逼真的制造技术创造出了可以工作的复杂电路。

然而,一个研究小组(同样来自斯坦福大学)演示了10nm器件是如何容易地生产出来的使用二硫化钼。但是,斯坦福制造的设备是令人印象深刻的,这是它们的生产方式以及它们的表现特征,这些特征可以比基于硅的设备更快。

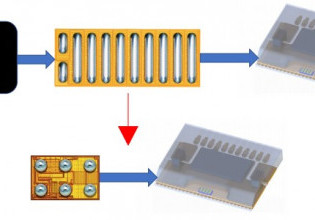

MOS2器件。图片礼貌斯坦福大学。

阅读更多

根据斯坦福的研究人员,当二硫化钼晶体管在10nm的等级时,在排水管和源之间移动的电子开始展览弹道导即电子在穿过材料时停止散射。这种散射导致了材料的电阻率,如果没有它,材料的电阻基本上为0。

因此,钼二硫晶体管中的电子可以通过不受半导体材料的影响,因此与其硅对应物相比可以更快地操作。埃里克流行(斯坦福大学的一名电子工程师)估计,在10nm的器件中,有五分之一的电子经历了弹道传导。然而,Eric Pop认为,如果半导体材料的质量得到改善,晶体管的尺寸减小,这种弹道导通数将会增加。这将导致更高速度的器件,可以传导更多的电流,而不像硅器件那样加热。

然而,这些设备不仅仅是小而快。它们可以很容易地使用与硅装置类似的技术制造。由于它们使用分层技术在大规模尺度上产生的能力,因此硅芯片非常成功,由此从硅的单个晶片(并且每个晶片可以产生数百个装置)添加或减去每个层。

斯坦福大学的研究人员通过在硅片上生长二硫化钼来制造出10nm的器件。然后,在半导体上生长一个栅极,首先沉积20nm的铝,然后让它氧化(收缩到10nm)。

概括

硅正在迅速达到其极限,但客户对权力的需求不断增加。在新材料需要进入并提供急需的处理能力之前,它不会很长。钼二硫化物装置在纳米尺度装置领域显示出许多承诺,但它们是否成为未来的半导体仍然不清楚。

如果一切都很好,那么硫化乳蛋白硫化物那么抓住?

这篇文章需要对标点进行认真的修改。