在这篇文章中,我们将从高层次的角度来看设计模拟ic的过程。

模拟IC设计与数字IC设计

模拟IC设计与数字IC设计有很大的不同。在哪里数字集成电路设计大多是在抽象的级别完成,利用确定门/晶体管级放置和路由的细节的系统和过程,模拟IC设计通常涉及将更个性化的焦点进入每个电路,甚至是每个晶体管的尺寸和细节。

此外,许多铸造工艺主要是为具有模拟特性的数字集成电路开发的,这就要求模拟集成电路设计人员利用工艺约束和更适合数字集成电路的特性来工作。

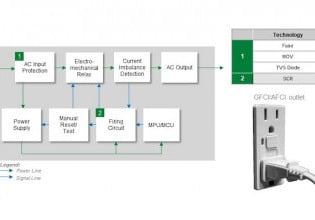

图片由罗尼B Chandran

设计规范

模拟设计团队通常从一组规格和功能开始,就像数字IC设计一样。在此基础上,使用各种功能的功能模型进一步缩小约束,并导致对设备大小、类型和其他流程特性的决策。这可能包括晶体管的选择,高级布置图规划,电感和电容技术的包含,以及IC和子电路所需的性能值。

架构硬件描述语言(AHDL),例如VHDL-AMS,用于在高级执行模拟,并确定子块的约束。也可以在稍后用于仿真的阶段开发测试台,但模拟设计人员也经常为其子电路设计开发测试台。

子电路设计、物理布局和仿真

有了这些细节,并根据模拟电路的复杂性,模拟设计团队通常会将子电路设计分配给个人。通过理想化的宏观水平测量来进一步确定子电路的约束条件和性能期望。

在此之后,这些宏观原理图被分解成基于铸造过程建模的电路元素原理图。对这些电路进行仿真和优化,然后开始物理布局过程。在寄生提取和布局后模拟之前,先进行布局和路由,然后进行设计规则检查(DRC)和布局与原理图的对比。

一个后布局模拟可能会揭示设计中的缺陷,一个重新设计、布局和模拟的迭代过程可能需要满足最终设计目标和提交集成电路用于封装。在整个芯片布局和模拟之前,子电路也可能经历它们自己的设计、布局和模拟过程,尽管任何一种方法都可能导致需要在封装之前重新设计电路。

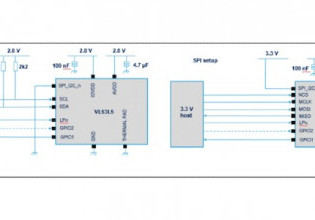

一个波形窗口的Cadence模拟环境的设计实例。截图使用萨阿德·拉赫曼和钦坦·帕特尔通过马里兰大学巴尔的摩县分校

模拟抽象级别

下面是模拟IC设计过程的抽象层次:

- 功能

- 行为的

- 宏

- 电路

- 晶体管

- 物理布局

模拟IC设计流程

与模拟IC设计相关的具体步骤可以细分如下:

- 设计规范

- 规范

- 约束

- 拓扑

- 试验台的开发

- 流程示意图

- 系统级原理图条目

- 架构HDL模拟

- 块高密度脂蛋白规范

- 电路级原理图输入

- 电路仿真与优化

- 物理流

- PCell-based布局条目

- 设计规则检查(DRC)

- 布局与示意图(LVS)

- 寄生提取

- 布线后仿真

- 胶带掉

在下一篇文章中,我们将讨论射频集成电路的设计。