编码的状态

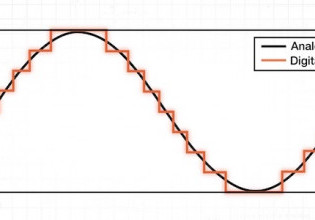

我们在上一篇文章中介绍的前面的示例并不是从头开始的:状态的值已经被分配了。结果是,当你设计一个状态机时,你可以选择给每个状态分配哪些值,更重要的是,如何编码你的状态。

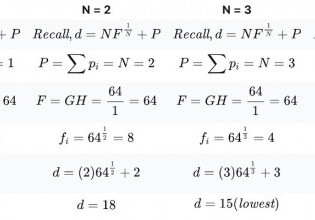

状态机有几种编码,最流行的是二进制编码、灰色编码和单热点编码。选择使用哪种编码对人类来说是一项困难的任务。这就是为什么最好让编译器为您选择它。我们将在下一篇文章中更多地讨论比较这些编码。

FSMs的设计

您现在可以使用上面描述的技术设计Mealy和Moore状态机,一旦您掌握了它,就会觉得很有趣。

但是,除了学校的项目,你多久会真的需要一个具有任意行为的状态机,就像我们刚刚设计的那样吗?几乎总是!它一开始可能不明显,但您可以采用自顶向下的方法将您的系统描述为一系列状态。这个序列可以画成一个状态图,或者写成一个状态表。一旦您获得了这种表示,您就可以自由地编写您的HDL代码了。

请注意,在我们的示例中,您可能会或可能不会使用输出变量y,这是可以的,因为许多状态机只是指示系统的行为,而这种行为可以在专用的状态用例中编写。

那么初始状态呢?

自传统逻辑集成电路时代(例如74LSXX TTL和40XX CMOS芯片)以来,设置初始状态一直是一个棘手的挑战。那时你依靠的是预设和清晰的您的人字拖的输入,它与一些开机复位信号绑定,以便在开机时始终设置所需的初始状态。

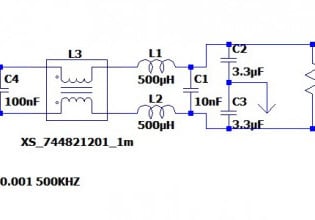

现在,对于fpga,关于是否应该在系统中使用复位输入信号作为这种上电复位信号存在争议。我们的带有复位输入的Verilog示例如下:

模块MyFSM (

输入时钟,

输入重置,

输入x,

输出y);

注册(1:0)状态;

赋值y = state[1]&state[0]&x;

总是@ (negedge clk)

如果(重置)

国家< = 2 'b00;/ /……或者你想要的初始状态。

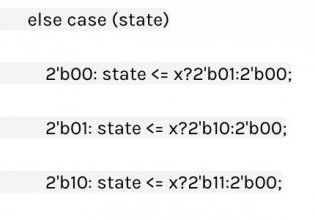

其他情况(状态)

2'b00:状态<= x?

2'b01: = 2'b00;

2'b10: = x?2'b11:2'b00;

2'b11:状态<= 2'b00;

endcase

endmodule

争论的原因是,大多数(但不是所有)FPGA将其配置内存实现为静态RAM(通常称为SRAM),这是易失性的,并且使用外部非易失性内存设备在开机启动过程中将配置复制到FPGA中。这个启动过程通常会启用Verilog最初的块是可合成的!

这意味着,当语言中有初始化方法时,您可能不需要重置输入信号来初始化变量。使用原始的Verilog示例,只需要额外的一行代码:

初始状态<= 2'b00;//

…或者你想要的初始状态。

然而,并不是所有的fpga都将其内部配置内存作为SRAM来实现。一些fpga(如Lattice MachXO2家族)有一个内部的非易失性配置内存,所以不需要启动任何东西最初的不能用于合成的块,并且仅对初始化测试平台模块有效。

的主要原因最初的一般来说,不能综合的块是Verilog用于许多目标技术,包括ASIC(没有启动序列)。无论如何,您应该始终考虑遵循FPGA制造商关于是否使用复位输入的建议,或者至少在决定使用复位输入时找到一个好的理由。

软处理器中的FSMs

您可能知道,所有cpu的控制逻辑在某个地方都有一个状态机。这些状态可以有描述性的名称,如获取、解码、执行和回写,或者它们可以简单地被视为执行周期,如周期1、周期2,等等。关键在于,CPU内核是Verilog中非常容易实现的FSMs应用程序。

如果您希望使用本文描述的技术在Verilog中看到软处理器的实现,请看一看吉米,8位软处理器我是教计算机架构的。

在Verilog中编写一个FSM乍一看可能有点吓人,但是如果您让合成工具帮助您输入代码作为case语句,您就可以轻松地启动并运行您的应用程序。

在后续文章中,我们将探讨使用不同的开发工具在状态机中使用不同beplay体育下载不了的编码时所产生的硬件差异。

恕我直言,您应该始终在FPGA代码中设置初始状态,

在我所知道的工具中,如Quartus和Vivado,如果你不指定初始状态,工具会为你选择初始状态。

如果你不设置初始状态,那么模拟就会很痛苦。

对于复位信号,

这是另一个问题。

如果复位只是为了模拟,请参见上面关于初始状态的介绍。

如果重置只是为了让您以已知状态在系统中启动,那么您需要它吗?

如果机器是“安全的”,机器总是会回到“初始状态”,那么让它在任何状态下启动并自行解决又有什么害处呢?我听到的反对意见是,那驱动马达的输出呢,它们可以把我的机器带到任何地方,

我的想法是,

您有这样的输出,您需要在输出上有一条控制线

假设您有一个处理器作为管理器,那么处理器将不会释放输出,直到它从电源获得良好的信号,并且安全锁到位,为什么FPGA不一样呢?FPGA无疑是从处理器上编程的,所以当处理器配置好并准备好时,FPGA会向处理器发送良好的信号。

出于一个简单的原因,我通常对所有状态机进行重置——可能有必要将设计返回到初始状态,而不需要电源循环设备。无论是在内部执行软复位的能力,还是在外部设备的命令下,或者只是对错误情况作出响应,许多设计都需要在功率循环以外的情况下进行复位。如果您以后决定不需要这种类型的重置,您可以用一行代码优化整个重置网络,将重置信号设置为恒定的非断言状态。但是,如果您不包括重置逻辑,然后发现您需要它,您需要重写大量的RTL代码。