在这篇文章中,我们将考察的最简单的版本基本集成电路放大器拓扑。

支持信息

微分或单端?

介绍性的研究活跃的电路通常花大量的时间标准的单端放大器configurations-e.g。同源性疾病、common-gate射极跟随器。这是一个值得努力熟悉晶体管的操作,小信号分析和放大器的特点。但是,实用单端放大器配置的值是一个不同的出生在实际上,差动放大器主宰现代模拟集成电路。有几个原因:

- 差动放大器应用获得,而不是一个输入信号区别两个输入信号。这意味着一个微分放大器自然消除噪声或干扰存在于两个输入信号。

- 差动放大也会抑制共模信号,换句话说,存在一个直流偏置,在这两个输入信号将被删除,和增益将仅适用于感兴趣的信号(当然,前提,感兴趣的信号不存在在两个输入)。这是特别有利的背景下,集成电路设计,因为它不需要笨重DC-blocking电容器。

- 发生在一对差动的减法电路很容易把负反馈放大器,如果你读过负面反馈系列,你知道负面反馈是有史以来最好的事情发生在一个放大器电路。

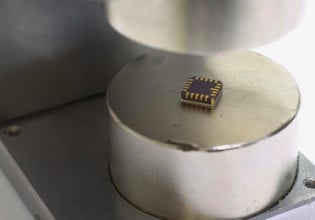

只有合理的期望这些好处是伴随着重大缺点,但IC制造的性质使得微分配置几乎完全有益的。两个问题1)更高的组件数量和2)对称分量特征的重要性。1号你可以忘记,因为添加更多的晶体管,集成电路的成本可以忽略不计。至于2号,IC技术是非常好的在芯片内实现组件间的一致性(这种一致性是被称为“匹配”)。

在本文中,我们将探索基本MOSFET差分放大器配置beplay体育下载不了的概念讨论和模拟(即。,而不是太多的数学或复杂电路分析)。因为这个主题相关的主要集成电路实现,我们将使用一个NMOS模型是特定于0.35µm CMOS技术;各种LTspice文件和一些可以找到相关信息在这里。

一双场效电晶体

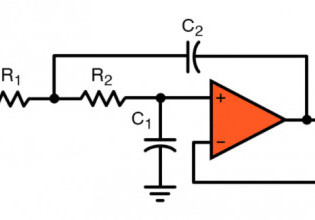

这是电路:

.jpg)

请注意以下几点:

- 在现实生活中,电流源符号将取而代之的是一个生成一个恒流电路。(参考基本的MOSFET恒流源为更多的信息。)然而,我们要保持好和简单的介绍分析,所以在我们模拟我们将使用一个理想的电流源,而不是恒流电路。

- 一个实际的IC实现电路将取代电阻的电流镜功能为“有功负载。”However, if our goal is to understand the functionality of the differential pair, I think we should start with the resistor version.

- 微分对都是关于平衡。因此,为获得最佳性能必须匹配电阻和场效应管。这意味着两场效应晶体管的通道尺寸必须相同,R1必须等于R2。两个电阻的阻值选择称为RD(d雨阻力)。

直流分析

让我们确定电路的偏压条件下,当输入都停飞。

.jpg)

我两个漏电流之和D1和我D2必须等于我偏见。我们也知道这两个漏电流是相等的,因为在这种理想化的分析,两部分的电路是相同的。因此,

\ [I_ {D1} = I_ {D2} = \压裂{I_{偏见}}{2}\]

假设目前的晶体管饱和。漏极电流饱和状态的方程如下:

\ [I_D = \压裂{1}{2}\ mu_nC_{牛}\压裂{W} {1} (V_ {GS} -V_ {TH}) ^ 2 \]

(我们将在本文中忽略通道长度调制。)漏极电流已经建立了由电流源()和盖茨与地面节点;这意味着创建一个电压源将解决一切价值gate-to-source电压(VGS)对应于我的漏极电流偏见/ 2。我们会通知仿真算出来。输出电压更容易:计算电阻器上的电压降(我偏见/ 2)×RD,然后减去从正供应电压降。这是一个例子:

.jpg)

输出电压。源电压似乎是合理的考虑到阈值电压(VTH这种香料模型是约0.5 V);仿真是告诉我们,VGS对应的漏极电流250µA 0 V - (-725 mV) = 725 mV,大概是225 mV VTH。

让我们回到我们的假设对晶体管的饱和(又名“活跃模式”)。MOSFET放大器需要保持其传输特性的饱和部分,因为获得更高和更稳定的饱和区域相对于线性区域。为了确保饱和,漏极电压必须高于门电压减去阈值电压:

\ [V_ {DS} \组V_ {GS} -V_ {TH} \ \ \ Rightarrow \ \ V_ {GD} \ leq V_ {TH} \]

在这个例子中,漏极电压(又名V出)固定在2.05 V。这意味着我们有一个限制V在:共模输入电压不能超过2.05 V + 0.5 = 2.55 V,因为当输入电压达到VTH漏极电压伏以上,MOSFET进入线性区域。

模抑制

让我们做一个快速的模拟向自己证明微分对不会放大共模电压。这是电路:

.jpg)

正如你所看到的,即使有1 V共模输入,输出电压仍在偏压- 2.05 V。一个简单的概念解释模抑制行为如下:输出电压的大小是由漏电流,输入电压。只要两个输入电压是相同的,固定的偏置电流是均匀地分成两个晶体管,从而V着干活和VOUT2不改变。

还要注意gate-to-source电压是相同的(因为漏极电流没有改变),虽然源电压增加,以弥补这一事实现在在门口1 V代替地面。

微分增益

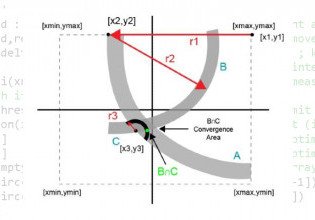

你能理解这个电路的微分行动如果你记得以下:

- 我D1+我D2=我偏见

- VS1= VS2

如果问的电压在大门口1高于电压门口问2,VGS1还必须高于VGS2,因为两个晶体管都有相同的潜在源终端。gate-to-source更高电压意味着更多的漏极电流,但漏电流之和仍same-thus,我D1增加我D2降低,这将导致相应的减少V着干活V和相应增加OUT2。例如:

.jpg)

我们将完成这篇介绍性模拟微分小信号响应的分析和比较模拟获得的理论获得。让我们共模电压回到0 V,然后应用1 mV正弦波的门问1:

.jpg)

我们将定义与V输出电压着干活- - - - - - VOUT2;这双打获得相对于仅使用V着干活或VOUT2,也消除了与偏差相关的直流偏置电压。这是一个阴谋与V三机一体和微分输出电压:

这里我们有一个输出幅度10 mV和一个输入振幅1 mV;因此,我们的模拟微分增益是10。理论微分增益的公式

\[现代{diff} = g_m \ * R_D \]

在g米可以计算如下:

大概{2 \ [g_m = \ \ mu_nC_{牛}\离开(\压裂{W}{1} \右)I_D} = \√6 {\ mu_nC_{牛}\离开(\压裂{W}{1} \右)I_{偏见}}\]

µSPICE模型n= 148.2厘米2/ V·s和t牛= 7.754×109。我们可以计算C牛作为

\ [C_{牛}= \压裂{\ epsilon_{牛}}{t_{牛}识别}= \压裂{3.45 \ times10 ^{-11} \ \压裂{F} {m}} {\ 7.754 * 10 ^ {9} \ m} = 4.449 \ times10 ^{3} \ \压裂{F} {m ^ 2} \]

因此,

\ [\ mu_nC_{牛}= 148.2 \ \压裂{厘米^ 2}{\ cdot s} \ * \离开(4.449 \ times10 ^{3} \ \压裂{F} {m ^ 2} \右)= 65.9 \ \压裂{\μA} {V ^ 2} \]

几乎完成:

大概65.9 {\ [g_m = \ \ \压裂{\μA} {V ^ 2} \ * \离开(\压裂{35 \ \μm}{\ \ 0.35μm} \) \ times500 \ \μA} = 0.00182 \ \压裂{一}{V} \]

完成:

\[现代{diff} = 0.00182 \ \压裂{一}{V} \ \ times5 \ kω= 9.1 \]

模拟计算= 9.1,= 10:我认为这是相当接近。

结论

基本的MOSFET微分对那些想深入研究的一个重要电路模拟集成电路设计。还有很多我们可以说这个电路,但我们现在就离开这里。在下一篇文章中,我们将研究的改进的性能可以通过使用一个活跃的负载,而不是漏电阻。

方程在页面的下一半应该VGD > = VTH,不是VGD≤VTH(左边是正确的)。我们总是需要确保gate-drain电压大于阈值电压,否则“开关”可以在源极和漏极之间被认为是开放的(即晶体管是关闭的)

从左边的又一面。

VDS > = VGS-VTH = > VTH > = VG - VDS = VG - VS (VD - VS) = VG - VD = VGD

我同意xk2006x,这是正确的在上面的文本。