了解异质和同质的公共汽车,特殊的IC套餐等等!

This article is a collection of special topics about the creation of schematic diagrams. The topics are ones I have carried around in my head for years. I hope you find them useful.

This article assumes experience with building schematic symbols and creating basic schematics.

高针计数零件

这是我从KICAD库中快速搜索发现的最高针计数符号。对我来说,这太密集了,完全不切实际。应该有一条反对这种事情的规则!我回到了一堆原理图,发现我的阈值约为100个销钉。超过100个引脚,我总是每部分创建多个单元。

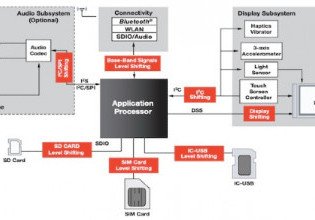

I break up a high pin count part by splitting the pins into functional groups. For example, an FPGA will have one unit for all the power and ground pins. Another unit will have all the pins associated with configuring the part. Then, there are multiple units for the I/O pins.

这是FPGA配置引脚的单元。

该符号可以放置在示意图中的任何地方。在这种情况下,它具有配置内存IC和用于编程和调试的JTAG连接器。床单上也是几个需要房屋的杂物。

这是带有电源和地面销钉的单元。

电源别针没有太多结构。两种类型的电动引脚分为两组:一组内部功率,另一组中的I/O功率。其他设备具有更复杂的功率结构,需要更多的组。该单元在带有电压调节器和电力监控电路的床单上。

I/O引脚分为四个单元。这是一个显示I/OS的25%的单元。

Altera (now Intel) parts often have internal interconnects with a prominent row and column structure. In this part, the I/O speed is faster for I/Os connected to row interconnects and slower for I/Os connected to the columns. Since this was a high-speed design, I needed to consider which signals were connected to rows or columns, and I created a symbol that helped me in the pin assignment. You can see that this unit is all “row” pins. In addition, the rows are further grouped together (ROW A, B, C, etc.). This arrangement indicates other timing characteristics inside the device.

考虑在可编程设备中对I/OS进行分组,以反映特定设计中零件的功能。如果我有助于对电路的设计和理解,则可以为自定义符号进行额外的工作。

等级制度

通常,示意图大于一张纸,可以通过两种方式组织或使用层次结构。平面原理图直接从纸张到纸张直接使用连接。一个信号通常从一个纸的侧面出现,并出现在另一张纸的侧面。层次结构在表中使用“分层块”来表示另一个表。通过连接到块来完成与表格的连接。表上可以有多个层次块。块和板的组织看起来很像计算机中的文件目录。通常有一个“根部”,就像根目录一样。

层次结构用于两个主要目的。首先,它提供了示意图内的逻辑结构,并以与信号连接一致的方式在板之间导航的方法。其次,它允许在纸上绘制一次电路,但使用多个引用同一纸的层次块多次重复。

使用层次结构是组织设计的有力方法。需要一些工作才能使这种结构感到舒适。但是,对我来说,它已经变得至关重要。我使用它太多了,以至于我从未在平面设计中使用直接的纸 - 向上连接。表总是通过层次块连接。微妙的效果是示意图对三维框图的外观。我喜欢此记录设计的方式,并使其快速易于找到东西。

Here is the root sheet of a 20-channel high-voltage amplifier board. Of course, it is not possible to see detail. However, perhaps you can see how the hierarchical blocks look like a block diagram.

我提供注释以列出每个块中的什么电路。单击进入块可以轻松找到一些东西。不是在这里,而是在其他设计中,我在根纸上包括没有电路连接的块,而是用笔记和图表引用表。使用这样的块,例如带有链接的目录表。

我注意到一个I2Cbus in the middle with three signals: I2CSDA, I2CSCL, and I2CINT. I wish I had been able to use a “heterogeneous bus” which is the next topic! I could have condensed three lines into one!

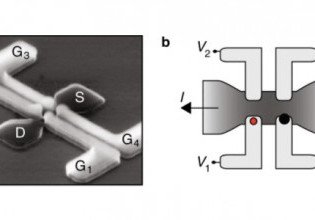

同质和异质公共汽车

All the schematic programs I know support collecting multiple, similarly named nets into a “bus”. The term originally came from bundling signals in a data bus or address bus. In the schematic below, this feature bundles signals with the name “SHDN” followed by sequential numbers. This is called a “homogeneous” bus.

在示意图的中间是spi与四个信号的接口:SS,SCK,SDI和SDO。他们是一个功能型组,将它们组合并使用一行和一个名称将所有人组合起来非常方便。一些示意图允许将信号分组为“异质”巴士。这种类型的巴士似乎没有标准化名称。Altium称其为“信号线束”。ORCAD使用术语“ NetGroup”。在鹰中,所有公共汽车都是异质的。Kicad正在开发此功能,并称其为“集体巴士”。

这是在eagle中为示意图中的四个网中创建的异质巴士。

In my opinion, a heterogeneous bus provides logical structure to the schematic and reduces clutter.

Special IC Packages

Mechanical designers have become quite clever in solving packaging issues related to smaller and smaller form factors and thermal management. However, some of their designs cause connections that should be shown on a schematic. I try to include in the schematic any package element that connects to a net. For example, a plated-through mounting hole for a connector shell or a thermal tab on a part that connects to GND or power should be in the schematic. Here are two examples of packages with features connecting to power or GND.

左侧的零件具有一个金属标签,通常将其焊接到板顶部的铜区域以散热。右侧的零件在底部有一个“裸露的垫子”,该垫子被焊接到铜区域。在这两种情况下,标签或垫通常都在IC内部电气连接。

This schematic shows how I handled the exposed pad for a voltage regulator using the package on the right.

Pins 1 to 5 are the normal pins. I added Pin 6 to represent the electrical connection to the exposed pad and connected it to GND. I also included 6 thermal vias that conduct heat from the top to the bottom copper areas. The vias are included in the schematic because they make an electrical connection. Here is the result:

Question: When is a 64-pin part not a 64-pin part?

回答: When it is an “E64” package.

在为此部分构建符号时,您会立即看到该部分没有地面别针!英特尔论坛上的一位评论者推测这是使用量子效应的尖端部分,不需要地面连接。好吧,不完全。地面是零件底部的裸露垫。这是底部的图纸,中间是垫子。

To deal with a part like this, just add a Pin 65 to the symbol. Then, connect it to GND in the schematic. Be sure to add a note on the schematic! The datasheet points out that the pad is only for electrical connection and has no thermal function. The PCB designer will need to know that!

奖励主题

“回到过去”示意图是手工绘制的,最常见于专业制图员。他们可能会不时地休息一下,并在示意图上涂鸦,以激发他们的想象力。这是Tektronix示意图的一个示例。

Image used courtesy ofvintageTEK

您是否曾经在示意图中添加了卡通或表情符号?

Have you ever used a non-orthogonal line for a net? Does your schematic program allow them?

If I remember correctly Ford Motor Co. calls their heterogeneous bus lines multiplex?

是的!谢谢。我最近的复杂设计使用EP3SL200F1517…它有1517个引脚。这将是遥不可及的,不可能包括在这些天绘制太多示意图的连贯示意图中。相反,我像你一样崩溃了。核心功率,配置,通信以及每个单独模块中的I/O银行。每个I/O银行的供应电源都包含在其各自块的顶部,因此看到每个银行运行的电压是微不足道的。

评估委员会提供的“示意图”具有一个巨大的矩形,其周长有1517针,每个销钉都呈标签。在其他页面上,您可以找到此标签,并最终找到其连接的内容。然后,在咨询了PIN描述并返回原始页面之后,您最终可以找到I/O银行正在运行的电压。像这样的“原理图”使我发疯。来吧,人们为您的工作感到自豪。

Let me say here that the purpose of the SCHEMATIC is to *schematically* explain to the user the functioning of the circuit. A handy additional function of computer generated schematics is that their output can also be handed directly to a layout program and populate a “ratnest” of the desired connections. The way many “schematics” are composed these days is nothing more than a graphical net-list, that could be just as well presented as a text file, with IC#, Pin# and signal name all in a linear list, and the router could figure it out. That would satisfy the routing program but would give almost ZERO information to the user about the functioning of the circuit. NOT the purpose of a proper schematic.

一个经典的示例是四分之一(或更多)放大器或逻辑门。它不是14/16针矩形,它是4个单独的物品,具有共同的电源。要正确显示在原理图上,您可以使用放大器(三角形)或逻辑门(OR/and/and/not/etc)的示意图。每个人都有一个标签,例如IC1A,IC1B,IC1C等。看到一个矩形,周围周围有一堆电线,这不是示意图。

在我的原理图上,诸如切换电源之类的东西不仅是矩形。盒子的内部具有手册中的块形图的草图。多通道ADC显示S/H,数字化器,输出序列器,模式选择,参考生成等。查看我的原理图时,您需要查看手册以找出芯片在做什么是减少的次数*几乎永远不会 *。这就是示意图的目的。您在这里所描述的是很长的路要走,应该认真考虑任何想要生成有用的示意图的人。

其他可以使用的东西是并行标记的引脚。您实际上不需要在原理图上单个芯片上显示137个地面销。库可以将它们连接起来,路由程序将包含所有内容,但是 *示意图 *与此众多相同的有目的的引脚获得了绝对零的其他信息。这是一个示意图,而不是接线图。接线图位于路由页面上。看看它是如何工作的?您在示意图页面上不需要的其他内容是包装类型,软件包的方向,无论该项目是否在顶部或底层等等。它们也在路由页面上。

可以创建更易于理解的原理图的其他多个事物,但并不是将所有芯片放入原理图页面上的空白矩形框中,可能是列表的顶部。保留这样的良好信息。