本文将审查可用于实现FSM状态的不同编码方法。

AAC的另一篇文章,在VHDL中实施有限状态机器,讨论如何在VHDL。

本文将审查可用于实现FSM状态的不同编码方法。我们将看到,对于给定的状态图,状态编码方法可以降低FSM的功耗或增加其时钟频率。

FSM的状态图表示

我们可以使用状态图来表示有限状态机(FSM)的操作。例如,考虑图1中所示的状态图。该FSM具有八个状态:闲置的,,,,R1,,,,R2,R3,R4,C,P1,和P2。此外,它有一个输入,mem和一个输出,OUT1。根据图,FSM将为即将到来的时钟滴答选择其下一个状态。

图1

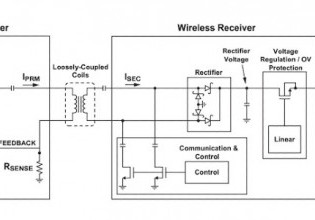

图2显示了可用于实现图1的FSM的框图。n记忆元素显示在虚线框中,以存储系统的当前状态。标有“生成下一个状态的逻辑”的框是使用触发器(FF)的输出和系统输入的组合电路来确定系统的下一个状态。

下一个状态将在下一个时钟刻度上加载到FFS集中。标记为“生成输出”的框,接收系统的当前状态并生成输出信号。请注意,由于“生成输出的逻辑”仅由系统的状态(而不是输入)驱动,因此我们有一个摩尔州立机器。

图2

二进制编码以实现FSM

在图1中,我们有八个不同的状态。我们需要多少个触发器来代表这八个州?

要代表八个州,我们至少需要三位。表1显示了编码这些状态的一种可能方法。这种方法称为二进制编码。

表格1

该表示形式导致图3所示的框图。

图3

假设三位字符串Q3Q2Q1代表表1的三个位。例如,当FSM的状态为R3,我们有Q3Q2Q1 =“ 011”。图3描绘了三个电容器(CPAR1,CPAR2和CPAR3)。这些电容器充当电路中存在的寄生电容的总元素表示。该寄生电容是由电路互连以及生成下一个状态和输出的组合电路的输入阶段引入的。

让我们更仔细地检查图1和图3。根据图1中的状态图mem = 1,每个时钟刻度都会使FSM从一个状态转到另一个状态。状态由图3中的三个触发器表示,因此在每个时钟刻度时,Q3Q2Q1的值会更改。这意味着CPAR1/CPAR2/CPAR3电容至少需要充电或放电。例如,考虑FSM从状态开始的情况闲置的而且,经过几个时钟的滴答声,到达州P2。在这种情况下,电容器CPAR1将收取四次(请参见表1)。同样,CPAR2和CPAR3将分别收取两次和一次。

每次必须收取电容器时消耗电流。因此,图3的电路所消耗的部分功率源自在FFS输出处看到的寄生电容。我们如何减少该电路的功耗?一种方法是减少我们必须收取寄生能力的次数。我们可以重新排列表1的三位分子分配以减少FF输出的过渡数量吗?实际上,这是可能的,解决方案称为灰色编码,在表2中使用。

表2

灰色编码可以减少功耗

使用表2的灰色代码,在相邻状态之间移动时只有一个位更改。现在,当FSM从状态下去时闲置的到国家P2,最低的一点将被收取两次,第二位和第三位仅收取一次。(将其与上述所需的四个,两个和一个充电事件进行比较。)因此,我们可以使用灰色编码来减少FSM的功耗。

灰色编码非常适合图1中的FSM,因为对于给定状态,已知系统的下一个状态。但是,大多数情况下,我们不知道系统的下一个状态。例如:

图4。可以使用灰色编码的状态图。图像提供低功率CMOS电路。

在图4中,根据输入的值,S29之后的状态可以为S32或S30。对于这种情况,我们首先应确定哪个路径具有更高的概率。然后,我们可以根据较高的概率路径来设置灰色编码。

灰色编码可以减少故障

如上所述,灰色编码可用于实现低功率设计。该编码的另一个应用是保护异步输出免受故障。例如,假设我们使用图5的示意图来产生输出OUT1在图1的状态图中,该图假设二进制编码用于表示FSM的状态。

图5

现在,考虑图6中所示的波形,该波形对应于从P2(111)到空闲(000)的状态变化。

图6

当系统在P2,,,,OUT1高。在T1,国家更改为闲置的。两输入和门的时间延迟后,节点N2将为零T2。稍后,在T4,节点N1会很高。请注意延迟N1假定比N2因为N1由不在门后放置的三输入和门产生。

如图6所示,最终值OUT1将是一个(在T5);但是,从高到低到低的过渡T3。在图5中的电路中,发生不必要的过渡是因为二进制编码允许多个位同时更改。通过灰色编码,在相邻状态之间移动时只有一个位变化,因此故障不太常见。

我们已经看到,适当的状态分配可以减少FSM的功耗,并使其异步输出对故障弹性。还有另一种状态分配方法,即单热编码,可以简化图2中的“逻辑以生成输出”和“逻辑来生成下一个状态”块。输出和下一个状态更快。下一节将更详细地讨论此编码。

一壁编码

请注意,在一个时钟周期内,图2的组合电路(即“生成输出的逻辑”和“生成下一个状态”电路的逻辑)应产生其输出,以便FSM准备移至下一个状态即将到来的时钟滴答。

单热编码使这些组合电路更简单,从而减少了传播延迟,从而使FSM与较高的时钟频率兼容。权衡的是,单次编码增加了用于存储系统状态的FF的数量。例如,虽然二进制和灰色编码仅使用三个FF来表示图1的八个状态,但编码单速hot使用了八个FF(即每个状态一个flip-flop)。

表3显示了我们八态FSM的单热编码。

表3

为什么这会使FSM的组合电路更简单?因为使用二进制和灰色编码,我们需要使用逻辑门来将3位表示形式“解码”为八个状态之一,而一台壁编码没有任何解码 - 状态直接对应于一位。火爆”。

哪个国家任务是最佳的?

还有其他一些状态编码选项,但实际上,我们通常使用上面讨论的三个编码之一,即二进制,灰色或单速。

问题仍然存在:我们应该如何为给定的FSM选择最佳编码?

获得FSM的最佳状态分配是一个困难的问题,您可以在教科书中找到这种优化的理论有限状态机的合成:逻辑优化和有限状态机的合成:功能优化。实际上,FPGA合成工具可以利用专有优化算法来实现FSM的有效实现。如果您设置XST(Xilinx合成技术)fsm_encoding选项“汽车”,该软件将为设计中的每个FSM选择最佳的编码。

例如,考虑图7中所示的状态图。

图7

图7中FSM的VHDL描述如下:

1个图书馆IEEE;2使用ieee.std_logic_1164.all;3实体fsm_enco是4个端口(CLK,重置:in std_logic; 5 mem,a:in std_logic; 6 out1:out std_logic);7结束FSM_ENCO;8 FSM_ENCO的架构FSM_ENCO_ARCH是9 type state_type IS(idle,r1,r2,r3,r3,r4,c,p1,p2);10 signal state_reg,state_next:state_type;11开始12-在图1 13过程中的寄存器(CLK,RESET)14开始15如果重置='1',则16个state_reg <= idle;17 elsif(clk'Event and clk ='1')然后18个state_reg <= state_next;19结束如果20结束过程; 21 -- next state logic 22 process (state_reg, mem, a) 23 begin 24 case state_reg is 25 when idle => 26 if mem='0' then 27 state_next <= idle; 28 else 29 state_next <= r1; 30 end if; 31 when r1 => 32 state_next <= r2; 33 when r2 => 34 state_next <= r3; 35 when r3 => 36 state_next <= r4; 37 when r4 => 38 state_next <= c; 39 when c => 40 if a='0' then 41 state_next <= p1; 42 else 43 state_next <= r1; 44 end if; 45 when p1 => 46 state_next <= p2; 47 when p2 => 48 state_next <= idle; 49 end case; 50 end process; 51 -- Moore output logic 52 out1 <= '1' when (state_reg = idle or state_reg = p1 or state_reg = p2) else 53 '0'; 54 end fsm_enco_arch;使用XST合成此代码,我们获得以下合成日志:

===================================================================

*高级HDL合成 *

===================================================================

分析FSM

优化FSM

-------------------------------

状态|编码

-------------------------------

空闲|00000001

R1 |00000010

R2 |00000100

R3 |00001000

R4 |00010000

C |00100000

P1 |01000000

P2 |10000000

-------------------------------

===================================================================

如您所见,XST的优化算法选择了一击作为最佳编码技术。如果要选择编码方法而不是依靠合成器,则可以通过fsm_encoding选项。

概括

- 使用灰色代码,在相邻状态之间移动时只有一个位更改。结果,这种编码技术可以减少FSM的功耗。此外,灰色的编码使FSM弹性对故障的异步输出具有异步输出。

- 一壁编码简化了图2中的“逻辑以生成输出”和“逻辑来生成下一个状态”块”块。通过简化这两个块,我们可以生成FSM输出,下一个状态更快。

- 获得FSM的最佳状态分配是一个困难的问题,但是实际上,我们可以使用具有专有优化算法的FPGA合成工具来实现FSM的有效实现。

- 如果您设置XSTfsm_encoding“自动”的选项,该软件将选择设计中每个FSM的最佳编码。

要查看我的文章的完整列表,请访问这一页。