VLSI设计中的Elmore延迟模型

2020年11月11日经过Tosin Jemilehin在本文中,我们将讨论Elmore延迟模型,该模型提供了简单的延迟分析,避免了RC网络的耗时数值集成/微分方程。

在上一篇文章中,我们使用了VLSI设计中的晶体管尺寸线性RC延迟模型。我们得出的结论是,通过指出学者认为这种模型并不是最准确的文章。更准确的模型是Elmore延迟模型,我们将在此处讨论。

Elmore延迟分析模型估计了从源(根)到叶子节点之一的延迟,作为ITO路径中电阻的总和Th节点乘以分支末端存在的电容。它提供了简单的延迟分析,可避免RC网络的耗时数值集成/微分方程。

实施Elmore延迟

通常,大多数电路都可以表示为没有循环的RC电路。正如我们已经说过的,Elmore延迟估计了从源(根)到叶子节点之一的延迟,作为通往I的路径中的电阻之和Th节点乘以分支末端存在的电容。换句话说,从开关源(root)到i的传播延迟Th分支节点作为电容的乘积“ C我”节点的电阻和从源到节点的电阻之和r是。

\ [t_ {pd} = \ sum _ir_ {is} c_i \]

r是=从源到节点I的电阻总和

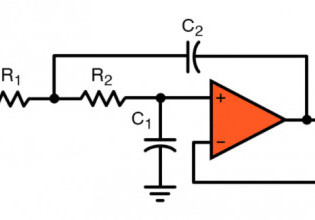

为了说明,让我们回想一下2ND我们在RC延迟模型中考虑的RC等效电路:

图1

V的Elmore延迟出去以t为tPD= r1C1+(r1+ r2)C2这类似于我们在上一篇文章中讨论的两次常数(TTC)近似模型的延迟表达式。

让我们考虑一个驱动程序-I.E。是一个充电或放出节点的门,或者换句话说,是连接到另一个门输入的门。就我们的示例而言,我们将查看一个驱动器的驱动器,该驱动器的单位尺寸是驱动M-ISDENICALITALE逆变器的驱动器。等效RC电路如图2所示。

图2

\ [t_ {pd} =(3W +3M)c \ frac {r} {w} =(3 +3 \ frac {m} {m} {w} {w})rc)\] \]

等式1

从公式1中,如果我们表示驱动器的扇出是负载电容(3MC)和输入电容(3WC)之间的比率,我们将得到以下内容:

\(h = \ frac {3mc} {3wc} = \ frac {m} {w} {w} \)

然后,我们可以将等式1重写为

\(t_ {pd} =(1+h)3rc \)

等式2

其中τ= 3rc。

寄生延迟和逻辑上的努力

让我们回顾一下RC延迟模型文章中给出的NAND门。如果设置了NAND门以驱动“ H”相同的NAND门,则意味着它将在负载电容值中看到附加的“ 5HC”电容,如图3所示。

图3。图像改编自CMOS VLSI设计(第4版)尼尔·H·E。韦斯特和大卫·钱玛·哈里斯

如果我们查看上升过渡的最坏情况(如图3(b)所示),PMOS晶体管将将输出节点y拉到高,而活动的NMO也贡献了寄生能力,从而减慢了这一过渡。

请注意,电阻“ r”沿着输出节点“ y”的路径充电。然而,由于跨它们没有输出路径,因此未考虑两个NMOS晶体管电路的电阻。这就是为什么它们仅对输出节点Y贡献6C电容值。

鉴于此,我们得到以下内容:

\ [t_ {pd} = r(9c+5hc+6c)\]

\ [t_ {pd} = r(15c+5hc)=(15+5h)rc \]

\ [t_ {pd} =(5+ \ frac {5} {3} h)rc \]

等式3

通过观察,我们可以看到延迟有两个组成部分:恒定部分,而延迟部分则在粉丝范围的“ h”方面陈述。

恒定部分称为寄生延迟,这是驱动其内部电容的时机(在这种情况下为5C)。等式2中逆变器的寄生延迟为1。

另一部分是努力延迟或者电力,现在是将负载电容驱动到驱动器电容的时候,有时也称为逻辑努力。同样,等式2中逆变器的逻辑工作为1,而方程3中NAND的逻辑努力为\(\ frac {5} {3} \)。

与逆变器相比,逻辑上的努力衡量最差的门是产生输出电流。这个概念对于分析任何标准基本逻辑门的延迟至关重要,结合可以将其抽象为逻辑门模块或功能块的负载。

下表显示了共同门的逻辑努力。

表格1。普通大门的逻辑努力

Elmore延迟的变化

Elmore延迟非常有效地计算,它可以深入了解上一篇文章中讨论的近似算法。当使用HSPICE模拟计算时,它还显示出良好的保真度。已经提出了进一步的改进,例如安装的Elmore延迟1以及改善的Elmore延迟2楷模。

但是,Elmore的延迟无法准确确定门的逻辑工作,这对于建模大型VLSI系统很重要。为了解决这个问题,我们将需要讨论一个新模型,以帮助确定如何在不增加晶体管大小的情况下保持寄生延迟最小。因此,在下一篇文章中,我们将讨论单个和多个路径的“逻辑努力”。

参考

- A.-S. ArifI.,Brian,N。和Chris,C。(2004年,6月28日)。拟合Elmore延迟:一个简单准确的互连延迟模型。EEE大规模集成(VLSI)系统的EEE交易,691-696。doi:10.1109/tvlsi.2004.830932

- Mutlu,A。和Serhan,Y。(2010年4月8日)。VLSI互连的改进的Elmore延迟模型。数学和计算机建模,51(7),908-914。doi:https://doi.org/10.1016/j.mcm.2009.08.024