本文将介绍一些在设计DC-DC降压变换器时可以使用的一般技巧。

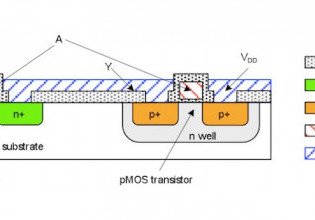

基本的DC-DC Buck变换器电路

在我们开始之前,让我们查看DC-DC降压转换器的电路:

Buck变换器的组件权衡

理解您所面临的设计权衡是很重要的。

为了帮助你,我开发了一个关于buck设计中“什么影响什么”的矩阵:

乔治·比纳的《什么影响什么》。

主要权衡是选择电感(与K型,即峰值到峰值与平均电感器电流的比率相反),输出电容和切换频率,以实现足够的纹波和瞬态响应。

设计者一定要利用稳压器IC制造商的设计工具来确定元件值和电路仿真。

了解你的电容器

- 确保电容器在操作频率下具有电容,并且知道其自谐振频率的位置。

- 陶瓷在宽频率下性能良好,但电容相对较低。通常,一种电容类型不能覆盖整个频率范围,而两种类型(例如陶瓷和电解)必须并联使用,陶瓷更接近电路。

- 电容器还损失了施加偏置电压的大量额定电容。

信任但要核实:芯片和组件

- 在由第三方制造的带有微小、未标记组件的pcb上,你必须相信填充板安装了正确的组件。确保你的信任没有放错地方。

- 如果您已将芯片发送到制造商进行故障分析,请不要处于非活动状态等待结果。这些天芯片质量水平非常高,这芯片对你来说非常不太可能。该分析也将花一些时间。同时,你可以找到真正的问题。

- 如果您正在使用数字芯片,请验证您所更改的设置实际上已写入芯片,而不只是写入GUI。

考虑测试和测量

- 不要认为直流电压是稳定的,没有验证的范围。

- 测量纹波的过程有很多过程 - 以适当的设备执行它是昂贵的。虽然最好使用花哨的差分探头,但您可以使用单端探头 - 只需确保接地线非常短,旁边连接V出去。

- 使用1x探头(您可以自己构建)。10x探头不会有您需要的敏感性。

HF尖峰通过电感的寄生电容耦合到输出。您可能需要减慢上部MOSFET的开启以减少振铃或dv / dt底部MOSFET的杂散开启,虽然这一叮当声。

分析输入电容

- 输入电容比输出电容更难理解,但它可能需要达到输入噪声要求,并确保您的电路不缺乏电流。

- 输入电容器具有大的纹波电流,达到50%的占空比,产生热量,并缩短盖帽的寿命。确保电流在其规范中。添加更平行时,存在基本权衡C在,因为越来越低的ESR将导致更高的纹波电流和更多的加热。为了真正降低输入纹波电流,你可能需要一个串联电感器。

- 由于占空比较高,电流从C在较高,导致更多V在在芯片前低头——如果V在已经很低了,因为你更接近跑进较低的V在限制——你可能需要增加C在在这些情况下。

提前思考PCB布局

- 了解当前路径的基础和高电流环的最小化。学校教授了很多关于前进电路路径,但没有关于返回路径的任何东西,这显示为完美的地面符号!制作布局,使得返回电流可以遵循它们的自然路径(最小化循环)。

- 保持低功率路径电感。通过它们的脉冲电流产生电压尖峰和辐射电磁干扰。高功率过孔是可以的,但应该了解它们的特性。

- 了解电路节点的阻抗水平,并对其进行相应的保护。例如,误差放大器的求和节点是高阻抗和对噪声敏感的-隔离它并使它变小。

- 尊重模拟地、数字地和电源地之间的划分,并提供自然的返回路径。星形接地避免了大的脉冲电流通过与敏感的低电平电路共用的接地路径。

知道(和尊重)你的极限

- 请确保您尊重热降额曲线-在高温下,最大电流和功耗总是从“标题”值降低。

- 确保销电压永远不会超过操作规格,两个引脚接地和引脚。例如,在其引脚到地面上的一个引脚激励一个引脚,但违反其引脚销格规格到不同的引脚可能会燃烧芯片。

- 注意控制芯片的最小/最大可控开/关时间,确保不要操作太接近其极限。

结论

要了解更多信息,请阅读我关于转换器设计中的常见故障以及如何排除这些故障的文章。