Xilinx硬件加速器与O-RAN推动5 g服务器性能

2020年9月21日通过艾德里安·吉本斯硬件加速是创建一个新的5 g吞吐量现实42 x 24 x编码和解码为选举委员会和HARQ行编码的改进。

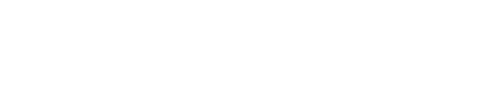

就在这个月,Xilinx揭开了T1,一个新的硬件加速卡设计将5克打开无线接入网络(O-RAN) fronthaul运输需求和计算强度,低密度奇偶校验(LDPC)检查L1网络堆栈。

作为PCIe电信加速卡Xilinx T1与机载SFP28笼子25 g光通信包括DDR4记忆HARQ查找和计算在一个紧凑的75 w形式因素。图像使用的镍板

结合partner-developed IP核O-RAN联盟,Xilinx 5 g说,它是优化服务器性能与T1作为PCIe加速卡。Xilinx T1卡是一个作为PCIe智能网卡x16创3基于Zynq Ultrascale + FPGA和Zynq RFSoC芯片组。

更高的数据速率要求硬件加速

5 g聚合数据的网络虚拟化软件导致吞吐量的限制,因为更高的数据速率由3 gpp定义只能克服硬件加速。Xilinx称其T1硬件加速器和商用现货服务器结果用于数量级更高的吞吐量和降低延迟。

T1参考设计包含合作伙伴IP核提供高性能网络函数的处理,有效地分割的网络功能从商业应用程序。图像使用的赛灵思公司

T1减轻了两个最密集的无线接入网络操作:1)fronthaul终止之间的无线电装置和分布式单元和2)L1前向纠错(FEC),混合自动重发请求(HARQ),和其他高PHY功能。

此外,改善ZUC Xilinx报告15到30倍,IPSec算法,这是包的一部分数据融合协议(PDCP)。

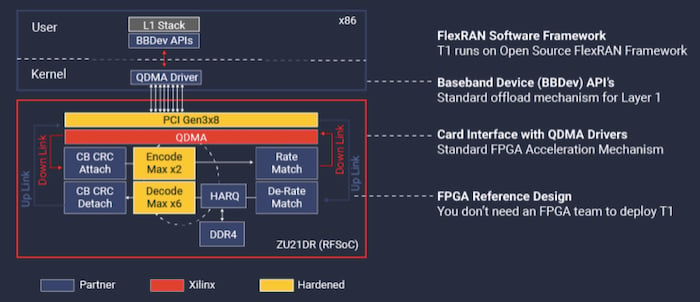

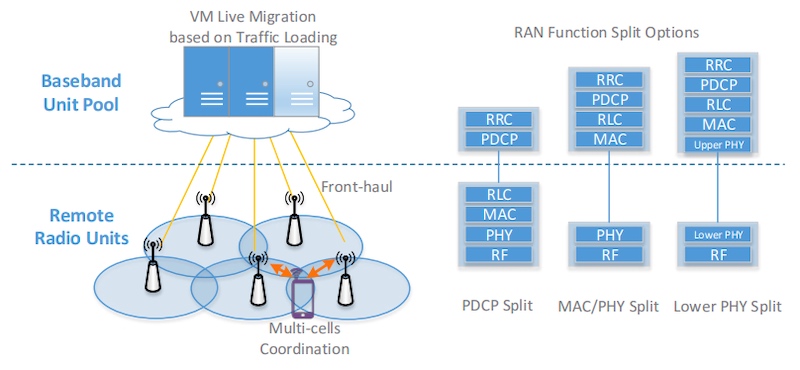

杰西卡为Keysight写作,描述O-RAN解决方案作为移动网络能够提高数据率为7 - 2分。

5克跑的功能分割。图像使用的Keysight技术

7 - 2分裂破裂PHY成high-PHY和low-PHY(选择7)的功能是分离广播单元(O-RU)和分布式单元(摘要)。然后,计算密集型操作(选项2)是由集中单元(O-CU)基带单元在那里我们可以找到Xilinx T1加速器。

O-RAN:开放接口,多供应商支持,更好的生态系统

在新闻稿的加速器,Xilinx公司的营销副总裁有线和无线,丹•曼苏尔说,“网络虚拟化的趋势和O-RAN给了我们一个机会Xilinx T1电信加速卡驱动下一步解集的网络标准,使我们拓展市场5 g的每一个角落。”

他解释说,该公司正在与它的生态系统合作伙伴提高Xilinx的硬件、IP和软件导致的创新和实现5 g O-RAN网络。”

Xilinx Ultrascale + FPGA生态系统非常符合开放硬件的O-RAN联盟的目标接口,据说促进供应商竞争和改善系统和低成本部署。T1提供预装行业伙伴FPGA参考设计,可作为PCIe与行业标准接口的接口通过基带设备(BBDev) API开源FlexRAN x86上的用户平台。

英特尔& ASTRI合作开发的基于云计算的虚拟化,利用FlexRAN分裂之间的远程无线单元(RRUs)和集中式的基带单元(BBUs)。图像使用的英特尔

硬件加速可能实现的关键5 g的吞吐量和低延迟目标电台fronthaul链接。通用处理器在网络边缘然后释放做的更重要的商业任务提供流媒体、游戏、和汽车服务。