Covid-19将聚光灯放在开源RISC-V核心,IP上

5月20日,2020年经过Antonio Anzaldua Jr.在这种流行病中的遥控器已经轻轻一点,并在RISC-v的美德上进行了光线,这刚刚获得了更频繁的途径。

Covid-19 Pandemic已经给出了RISC-V的新机会,以证明他们可以帮助工程师开发筹码而不担心资金。最近,几家公司已经开始提供RISC-V核心处理器,这将允许程序员在不支付专有硬件许可证的情况下建立复杂的设计。这些公司的许多公司的说法是扩大设计人员的资源,使他们能够为诊断,预防和治疗创新做出贡献。

在本文中,我们将简要触及RISC-V的优势 - 特别是在许多工程师感到从设计资源的完整广度中被切断时 - 并探索几个组织如何更容易地获得该工具。beplay体育下载不了

RISC-V架构

RISC(减少指令集计算)设计使硬件设计人员在功率效率,可靠性和远程支持方面更轻松地更轻松 - 但它配有一个崇高的价格标签。开发人员未获得RISC设计的访问,而无需满足英特尔,ARM和Micron等公司所需的专有硬件许可证。

另一方面,RISC-V是一个嵌入式核心处理器,可在自由,非限制性许可证下具有开放标准指令集架构(ISA)。根据RISC-V国际,RISC-V.为任何完整的自定义芯片开发带来新的设计工具,启动建设器,编程语言,稳定性测试和仿真设计。程序员可以设计自定义核心并下载免费标准核心评估开发套件,包括Verilog RTL和FPGA比特流。

RISC-V基金会批准过程跟踪规格

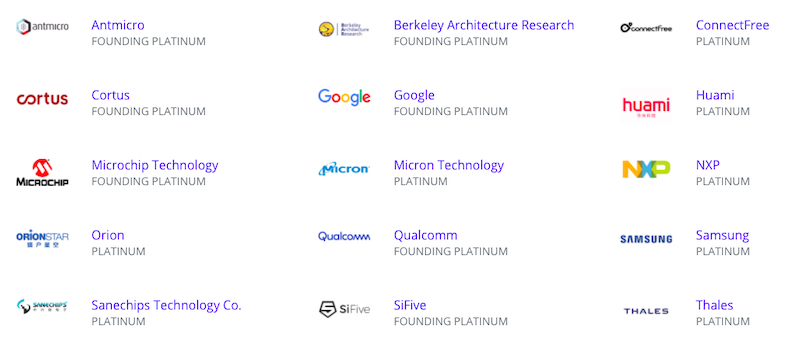

RISC-V基金会是由其专用成员控制的非营利性公司。他们有一个简单的目标:推动全球开发人员的免费和开放RISC-V ISA的采用和实施。

RISC-V基金会包含500多名成员,构建第一个开放,协作社区的软件和硬件创新者。使用的图像礼貌RISC-V基金会

本月初,基础宣布批准处理器跟踪规范。本规范将提供新的标准跟踪编码器算法。算法将允许硬件工程师在整个设计过程中执行核心处理器时预览指令。

这种跟踪规范对设计人员进行了尤为有助于,因为它在调试后,它被暴露准确,详细的活动痕迹,同时隔离有效的跟踪部分。RISC-V基金会有200多名成员,包括三星,谷歌,NVIDIA,西方数码,NXP,Micron,Qualcomm和Raspberry PI。

Sifive承诺在大流行期间开放对其知识产权

除了新的处理器跟踪规范之外,另一个RISC-V开发来自Sifive,它有承诺开放进入其知识产权(IP),所以设计师可以帮助打击Covid-19。

Sifive,成立于2015年,计划民主化进入定制硅,提高质量和减少市场时间。在这些前所未有的时期,Sifive提供了对其E21标准核心嵌入式处理器的访问。他们的希望是,设计人员将在MCU应用程序中使用此处理器,以获得需求的医疗保健设备,如呼吸机。Sifive表示,它的RISC-V核心IP是世界上最具硅部署的RISC-V解决方案。

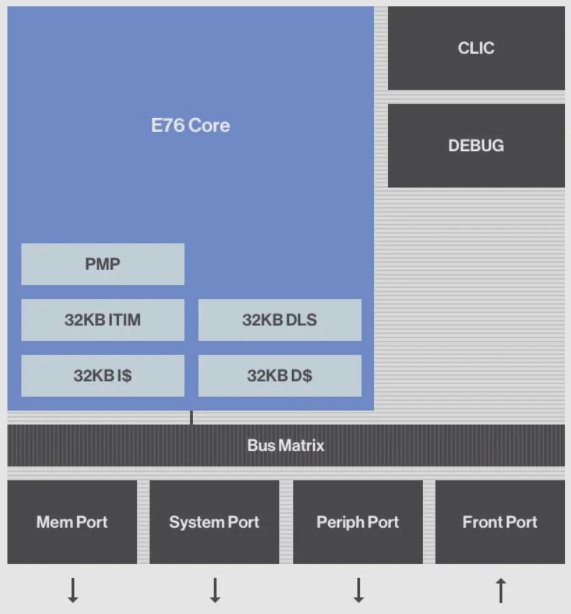

Sifive的“E”核心IPS之一的框图32位嵌入式核心-E76。使用的图像礼貌秀丽

与SiFive E21标准核心处理器相关联的软件将提供一个在线芯片设计工具,允许用户使用各种设计选项构建可自定义产品。

通过不需要提供此处理器,Sifive可能使设计人员能够构建用于救生设备的控制系统。他们的承诺也为科学家,工程师和开发人员提供了希望,以加速诊断,疫苗,治疗,医疗设备和软件解决方案来打击紧急健康危机的能力。

Chips Alliance无需推出硬件

与SiFive和RISC-V Foundation一样,接口,处理器和系统(芯片)联盟的公共硬件也在大流行期间提供援助。

芯片联盟是通过Western Digital-To Studity社区带来新的增强型Swerv核心EL2和EH2开发凭借加速医疗产品,人工智能(AI),物联网(物联网),移动设备和其他嵌入式应用程序的risc-v创新。

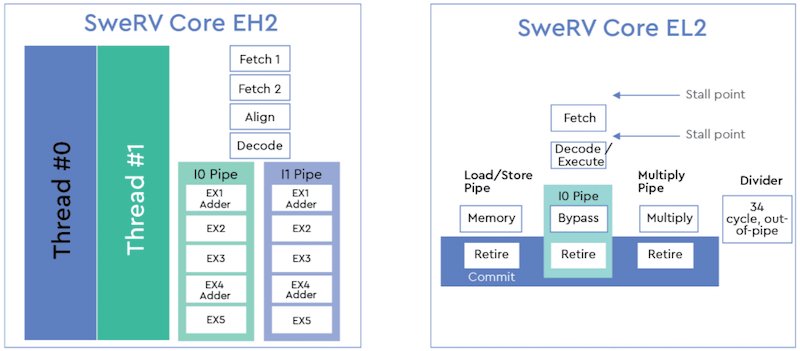

Swerv Core EH2和EL2图。使用的图像礼貌西部数据

本公告恰逢其一致RISC-V国际与GlobalPlatform合作,以简化IoT设备和处理器的安全性设计。

芯片联盟是一个开发和托管开源硬件代码,互连Internet协议(IP)和设计工具的组织。芯片联盟旨在提供无障碍的协作环境,以降低开发IP和硬件设计工具的成本。

Swerv Core EH2.是嵌入式RISC-V处理器,专为支持数据密集型EDGE,AI和IOT应用程序而设计的嵌入式设备。这el2.还利用RISC-V核,但对于超小而且针对诸如状态机序列和波形发生器等应用进行优化。

芯片联盟将是通过缩放托管在线活动讨论Swerv Core EH2和EL2。在此次活动中,芯片将免费为程序员提供软件支持和解决方案的使命。

RISC和奖励

在审查中,RISC设计的一些总体福利包括:

- 电源效率

- 简单,清洁板岩设计

- 模块化指令集架构(ISA)

- 系统稳定性

- 可变长度指令编码

- 轻松集成与FPGA可编程逻辑芯片

- 内置队列管理

由于程序员可以在32个寄存器的可访问数组中编写,因此RISC-V允许立即在提供信息管理时立即操作数据。设计人员无需为大量CPU任务寻求外部内存,降低整体能耗。内置队列管理是大多数现代处理器架构获得速度的速度 - 解码内部指令队列的一个很好的功能。

整个行业的组织和公司正在推动免费的RISC-V活动和资源。RISC-V可能会改变开发人员一起工作和协作 - 为设计人员创建开放硬件和软件生态系统的方式,以对Covid-19产生影响。