RISC-V的联合创始人,UNVELS对基于RISC-V的处理器进行了重大升级

7月25日,2020年经过Vanessa Samuel.作为RISC-V的联合创始人,Sifive对处理器的升级可能对自定义SoC设计具有显着影响。

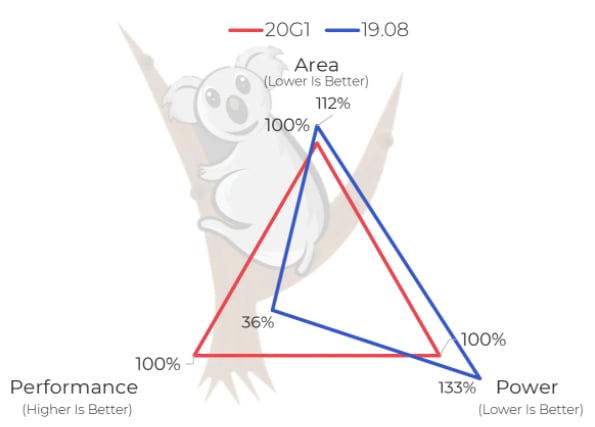

迅速度最近宣布其20G1发布,该公司RISC-V的Sifive IP核心处理器的扩展组合。一些改进措施集中在此版本中的功率,性能和面积(PPA)。

Sifive专门从事软件自动化工具,加快硬件开发过程。但是,由于公司的历史与RISC-V本身的历史为基础的基于RISC-V的核心处理器的更新尤为重要。由世界着名的RISC-V ISA的发明者创立(指令集架构),Sifive可能在开发这项技术方面具有独特的优势。

Sifive的历史与RISC-V

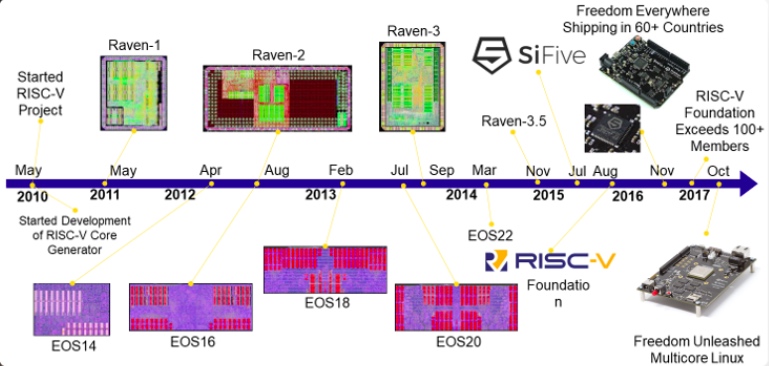

由于晶体管变得更加昂贵,设计且难以缩放,RISC-V(减少指令集计算机)的发明人决定了改变的时间。在2010年,他们成立了秀丽思维,利用开放采购和RISC-V架构以及定制的硅,以降低开发成本和设计时间。

RISC-V发明的演变,以及Sifive发明,2010年至2017年。图片(修改)使用秀丽

最初,他们的目标是广泛宣传RISC-V.现在RISC-V架构是世界知名的,目标是不断扩展RISC-V。虽然第一张磁带为28纳米,但SiFive现在有数百个磁带,从而实现了更广泛的应用。

20G1升级每个系列核心

这Sifive Core IP 20G1在每个不同的SiFive核心系列中引入了改进。第一个主要更新是,每个系列核心都已通过增强的实时功能升级。

20G1释放的功能。图片(修改)使用礼貌秀丽

在E3和E7系列中,Sifive表示,与RV32i相比,该地区已减少至11%。该公司还声称,与SiFive U74处理器(19.08)相比,Sifive U74(20G1)处理器上的性能均为2.8倍。

这允许改进的数据流以获得更多应用程序,包括AI。根据新闻稿,新的SIFIVE U74(20G1)处理器中的功耗也降低了多达25%的耗电量。

20G1在SiFive的自定义硅工具上建立

此Sifive 20G1发行符合其他几家公司通告,该公告旨在提高RISC-V的可扩展性。这些升级也有助于筹码的快速建设和装运。

例如,Sifive提供了Sifive自由工具套件,其中包含SDK,库和其他代码,以帮助设计人员在定制SiFive RISC-V处理器方面。此工具数据库也位于云上以进行远程访问。

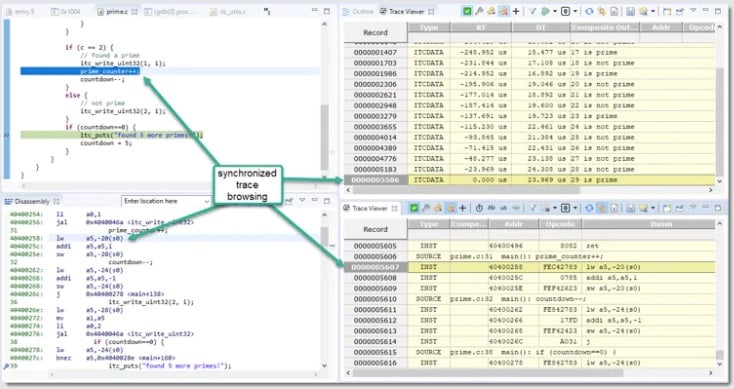

Sifive的Freedom Studio允许用户同步跟踪浏览。使用的图像礼貌秀丽

Sifive Insight是另一个有助于自定义过程的工具。它允许用户逐步追踪处理器的执行,并同时观察调试日志。Sifive 20G1版本在Sifive的洞察力中更新,这也支持ARM Coresight。Sifive断言,ARM Coresight将使用户更容易与其他SoC开发环境集成。

通过降低功耗,降低区域并提高性能,Sifive 20G1释放通过降低了SiFive核心IP线路的核心。此选项可能会对设计人员吸引,因为它是免费的,开放的ISA和用于定制硅的简化模板。

你有没有使用过RISC-V架构?它是如何影响自定义硅设计过程的?在下面的评论中分享您的经验。