IPs的目录包括安全核心、逻辑NVM技术、嵌入式分析和多核调试工具集。

Sifive是第一个开源芯片平台的发起者,是基于自由和开放RISC-V指令集架构(ISA)构建定制芯片所需的工具和核心。许多公司正在通过Sifive的IPS获得设计共享该模型旨在显著降低开发定制芯片所需的前期工程成本。

目标- Sifive的新首席执行官Naveed Sherwani将它置于它 - 是为想要开发自定义芯片的人创建一个级别的播放领域。以下是Sifive如何通过一次签署一个伙伴关系来简化自定义硅的开发。

Rambus提供安全核心

作为SiFive的DesignShare模型的一部分,Rambus将提供加密核心、硬件信任根、密钥供应和其他与安全相关的组件,SiFive的DesignShare模型有助于以较低的成本建立ip目录。

这将允许芯片开发人员轻松将安全核心嵌入Sifive的内容自由平台用于开发自定义系统上的芯片(SOC)。它将是保护物联网(物联网)端点和现场设备连接的关键特征。

eMemory的逻辑NVM IP

SiFive还将eMemory technology Inc.的基于逻辑的非易失性存储器(logic NVM)技术添加到其低成本IP目录中。这是一种嵌入式存储器解决方案,eMemory向半导体铸造厂、IDM和无晶圆厂设计公司授予许可证。

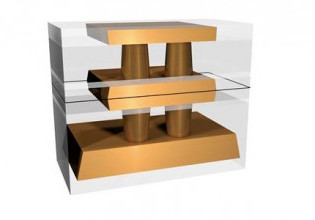

用于OTP、MTP和EEPROM内存块的硅IP。图片由eMemory科技公司.

该公司声称,其嵌入式内存IP已应用于消费、工业和汽车等应用领域的270多亿个芯片。其专有的硅IP技术包括NeoBit、NeoFuse、NeoMTP、NeoFlash和NeoEE。

UltraSoC的嵌入式分析IP

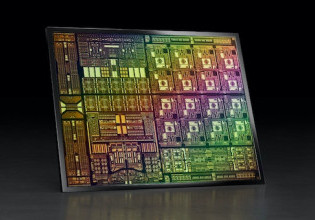

SiFive的Freedom设计平台基于开源RISC-V处理器内核,同时也积累了各种工具和接口。以UltraSoC为例,它提供与供应商无关的片上调试和分析工具。UltraSoC正在提供嵌入式分析IP为SiFive的设计共享计划。

芯片设计人员可以使用这种调试和跟踪技术来深入了解片上处理器块、定制逻辑和系统软件之间的交互。跟踪是开发人员在任何处理器体系结构上工作的基本要求;它允许他们详细地查看程序的行为,然后隔离错误并确定需要改进的地方。

从Lauterback调试工具集

微处理器开发工具供应商Lauterbach也宣布支持SiFive的RISC-V内核。劳特巴赫的TRACE32工具集将为SiFive提供调试功能E31型和E51.RISC-V核心IP,基于自由开放的RISC-V指令集。

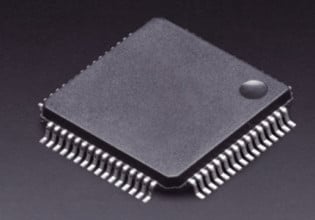

TRACE32工具集是规划支持USB等调试接口。图片礼貌Lauterbach GmbH..

该工具集在SiFive核的各个硬件线程上提供多核调试,从重置向量到分析启动代码和其他关键功能。

你对RISC-V有什么经验?有人参加本周的西部数字研讨会吗?在下面分享你的经历。