OpenHW集团宣布基于NXP IMX平台的多核评估SOC

2019年12月13日通过CABE ATWELL.核心- v底盘评估SoC将具有CV64A 64位核心和CV32E 32位协处理器核心以及3D和2D gpu。

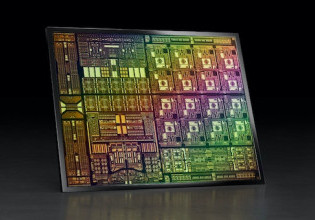

在今年的RISC-V峰会在加利福尼亚州圣何塞举行OpenHW集团宣布计划发布一个linux驱动的Core-V底盘多核评估SoC。SoC将基于恩智浦的流行i.MX应用平台。

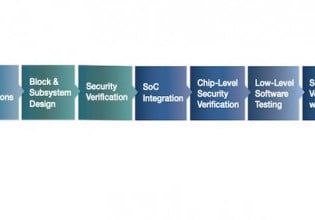

OpenHW集团寻求提供开源核心、相关IP和其他工具。从图片OpenHW集团

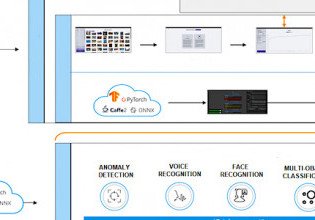

根据OpenHW集团的说法,Core V是“一系列基于RISC-V的开源核心,具有相关的处理器子系统IP,工具和电子系统设计师软件。”

(尚未设计的)SoC将在2020年下半年完成。

包括什么?

SOC将具有RISC-V核心IP 64位(1.5GHz)CV64A CPU以及伴侣32位CV32E协处理器。它还期望用CSI显示器包装3D和2D GPU,MIPI-DSI高速串行接口,以及相机I / O.

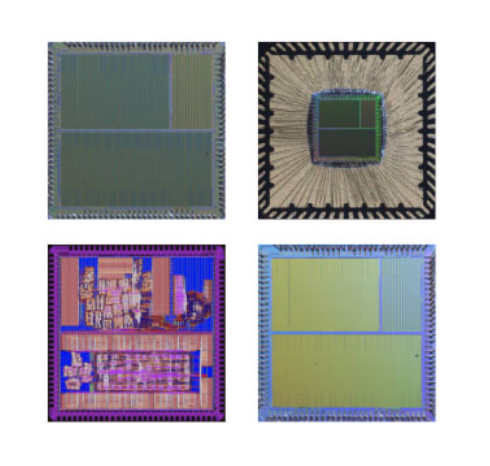

OpenHW Group声称他们在core - v系列的核心IP的硅和fpga优化实现中采用了最佳实践。从图片OpenHW集团

OpenHW集团还计划包括:

- 作为PCIe连接

- GigE Mac.

- USB 2.0接口

- 支持(LP) DDR4

- 多个SDIO接口

- 一系列外围块

- 硬件安全模块

并联超低功率(纸浆)平台

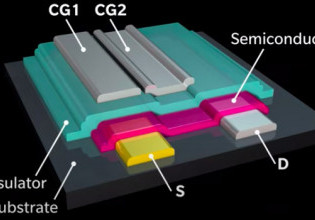

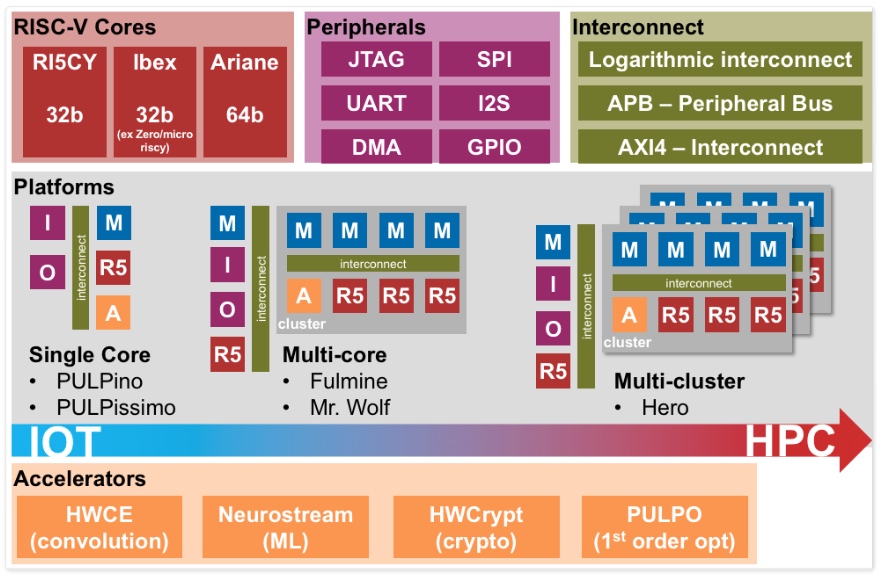

开源64位CV46A CPU和32位CV32E是在苏黎世联邦理工学院作为各机构纸浆(平行超低功率)平台。纸浆平台的设计目的是带来可扩展的、节能的硬件和软件系统,具有广泛的可调性能。

纸浆的平台。从图片纸浆平台

ETH Zürich解释道:“PULP的目标是满足物联网应用的计算需求,这些应用需要灵活处理多个传感器(如加速度计、低分辨率摄像机、麦克风阵列和生命体征监测仪)产生的数据流。”

RISC-V核心

ETH Zürich的工程师生产了几种RISC-V核心根据该项目,包括:

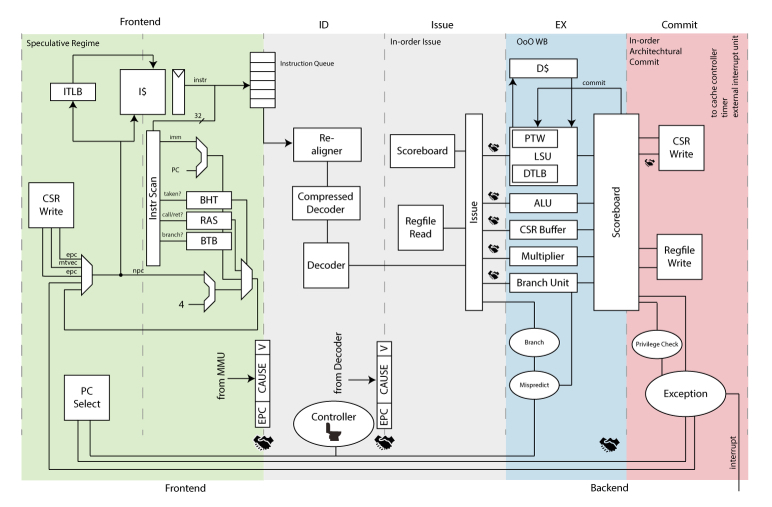

OpenHW集团基于其64位CV46A CPU在ETH的Ariane处理器上,这一级别的能效和可扩展性转移到Core-V底盘评估SoC。

基于RISC-V的Ariane CPU。从图片Github,阿丽亚娜文档

32位的CV32E也借用了ETH的RISCY (RV32IMFCXpulp) RISC-V 4级核心IP CPU,这提高了信号处理应用的性能。

在最近的一次新闻发布会上,OpenHW集团董事长兼NXP软件工程副总裁Rob Oshana表示:“NXP很高兴能够利用我们世界级的i.MX平台,成为CORE-V底盘项目的关键贡献者。我们认为CORE-V底盘项目是OpenHW Group开源RISC-V核心用于高性能嵌入式处理的自然演变。”

会员和合作伙伴

除了恩智浦,其他加入OpenHW集团雄心勃勃的计划的科技公司还包括阿里巴巴、华为、Silicon Labs、Mythic、OneSpin、Metrics、Imperas、UltraSoC等。

OpenHW组成员。从图片OpenHW集团

OpenHW集团也吸引了一些合作伙伴来推进他们的项目,包括Eclipse基金会、IBM Cloud、Fossi基金会、Publitek、普华永道和Norton Rose Fulbright等。

要求参与

Core-V底盘评估SoC将成为进一步多核评估SoC的基础。OpenHW集团表示,即将发布的平台是一个公开的呼吁,呼吁业内其他人士加入他们的项目。

openenhw集团首席执行官Rick O 'Connor表示:“CORE-V Chassis项目将有助于验证,利用开源硬件、IP和工具的精神,可以实现真正的硅开发。”

“随着2020年下半年SoC功能评估的完成,我们将证明,开放硬件思维与当今任何封闭源替代方案一样有能力和可靠。”