将晶体管缩小到下一个最小节点通常听起来像是一种简单的方法来提高IC性能。然而,实际上,扩展为IC设计人员引入了许多困难。具有缩放最值得注意的挑战之一是泄漏电流突出增加,这显着导致整体芯片功耗。

NMOS设备中的亚阈值漏电流。图像使用的是研究的礼貌和Udaiyakumar等。

因此,在全数字设计中,低泄漏技术越来越受到人们的追捧。最近的一个例子是,光谱设计与测试(SDT)上周声称其低泄漏SRAM为MMWAVE应用产生了高性能-具体解决毫米波天线公司Mixcomm的5G波束形成前端ic的大波束形成数据存储需求。

SDT的SRAM建立在45nm的RFSOI过程中,SRAM还使用专有的存储方法,包括基于源偏置设计技术的低功耗模式,以最大限度地减少泄漏。

除此之外,设计师还如何应对漏电电流增加带来的现代挑战?

漏电流的兴起

随着碎片缩小,漏电流 - 而且具体地SubThreShold泄漏 - 成为IC中的功耗突出的源泉。当开发人员缩小晶体管时,他们也倾向于缩小电源电压,以使动态功耗最小化。

然而,扩展电源电压对速度产生负面影响电路性能。克服这一点的常见方法是相应地降低阈值电压。随着设计人员降低阈值电压,它们会降低亚阈值区域 - 结果更频繁地漏光更频繁的间隔。

这就是为什么大多数开发商都停止了降低供电电压的原因:在某个点上,电压亚阈值泄漏的增加不值得减少动态功耗。

随着芯片的小型化,静态功耗变得越来越重要。图片由爱特公司

积分的增加是阈下泄漏变得如此突出的另一个原因。单个晶体管的亚阈值泄漏通常在皮安(E-12)量级。然而,一旦数十亿个晶体管加到一个芯片上,每个晶体管的漏电流的总体贡献就开始显著增加。

例如,如果每个晶体管都表现出10Pa漏电流,并且IC中有100亿晶体管,单独渗漏的总消耗将出现在100 mA。

绝缘体的技术

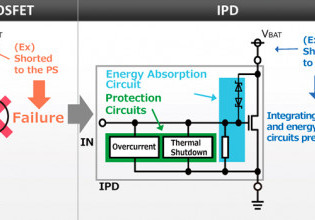

半导体工程师开发的另一种技术是将漏电流的影响降到最低绝缘体(SOI)技术。

传统散装MOSFET(左)与完全耗尽的SOI(右)。图片使用了STMicroelectronics的礼貌

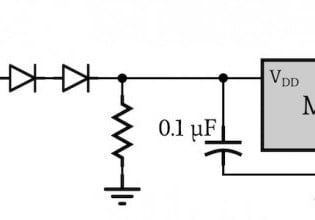

在SOI设计中,绝缘层直接放置在通道下方,从通道隔离身体。从通道中隔离身体的隔离率为许多益处,包括降低源和漏极之间的寄生电容。

重要的是,SOI技术还显著降低了泄漏电流,因为绝缘体限制了电子从源流向漏极,消除了通过机体的泄漏。

低泄漏作为流行的价值主张

考虑到功耗和泄漏电流之间的关系,业内许多公司和研究人员将低泄漏作为产品发布的一个关键价值主张也就不足为奇了。例如,Magnachip Semiconductor最近宣布了LDO线性稳压器据说,在深度睡眠模式下提供75 UA的低漏电流,延长电池寿命和效率。

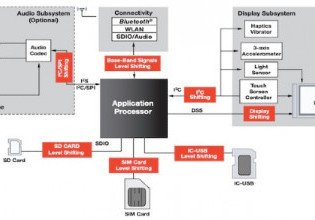

新的Magnachip LDO线性调节器是为智能手机设计中的基于UFS的多芯片封装而构建的。图片使用礼貌magnachip半导体

此外,École Polytechnique Fédérale de Lausanne (EPFL)和IBM欧洲研究中心的研究人员最近创建了所谓的基于硅的混合装置,将传统MOSFET与III-V隧道FET合并。参与研究员Clarissa Convertino报告给TechXplore,“隧道FET在低电压水平下提供较低的泄漏和良好性能,而MOSFET更快(在相同的尺寸和偏置)上并提供更大的电流驱动器。”

她继续,“除了单个掩蔽和外延步骤外,开发的制造流程对于两个设备相同,用于制造真正的混合逻辑块。”

在你的设计中如何防止漏电?你是否看到这一既定的设计原则在最近几年变得更加紧迫?请在下面的评论中分享你的想法。