随着5G时代的开始和摩尔定律的终结,多芯片封装可能成为一种内存解决方案

2020年10月26日通过史蒂夫asrar随着5G速度和存储需求与摩尔定律的终结发生碰撞,芯片制造商开始转向多芯片封装,以节省空间和电力。

5G技术预计将提供不到10亿美元的无线通信1毫秒的延迟和高达现有4G网络50倍的吞吐量。

这种速度将为令人难以置信的多媒体和视频体验奠定基础。然而,充分利用这些能力需要高性能的内存系统,能够跟上5G的速度和存储需求。

5G需要高性能的易失性和非易失性存储器

为了让5G的快速下载成为现实,我们需要一个大容量、快速存储的设备。以超高清内容流媒体为例。在这种情况下,我们的移动设备将需要在后台暂时缓冲视频。

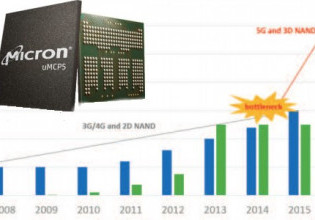

这需要一个大内存,读写操作和网络一样快。下图说明了二维平面NAND闪存不能满足当今无线通信的需求。

移动设备写入速度的增长与网络速度的增长是同步的。图片由微米(PDF)

克服闪存存储瓶颈的一个短期解决方案是3D NAND技术,该技术将多层存储模块堆叠起来,以增加内存容量和性能。

高性能闪存只是5G内存挑战的一半。即使是基于lpddr4的芯片组也将被推到5G设备处理海量数据的极限。没有改进的RAM内存,我们的视频分辨率会更低,延迟更令人沮丧,功能也有限。

什么是多芯片封装?

当我们到达摩尔定律的终结在美国,我们需要依靠其他技术来提高电子系统的性能。这些技术之一可能是多芯片封装,它将不同的芯片以堆叠的方式放置在同一个封装中。这种打包技术最近的一个例子是三星的3D IC技术。

下图显示了一个堆叠的产品与三个不同的模具粘合在另一个上面。

一个多芯片包的例子。图片由绿诺科技Micheloni

注意键合线是如何将每个模具的IOs连接到封装基板上的。

多芯片封装(MCP)允许我们在同一芯片内拥有不同的存储器类型——例如,非易失性闪存和易失性dram。MCP技术可以实现高密度、低成本的内存解决方案,在更低的功耗下提高性能。

此外,通过卸载系统单片机的嵌入式内存,MCPs可以简化设计过程。在功率效率方面,它是可能的移除电源到非活跃的模具的MCP,而其他模具在包中操作。这个功能支持新的低功耗睡眠模式。

一般来说,MCP内存中的非易失性内存用于应用程序的启动、操作系统和其他关键代码的执行。易失性存储器作为高速临时存储器。

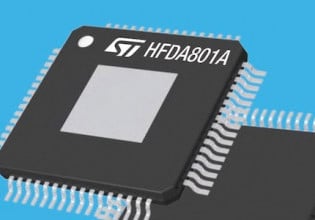

美光新的多芯片DDR5封装,uMCP5

美光最近宣布了一款新的MCP存储器uMCP5它将低功耗的DDR5 (LPDDR5) RAM和最新一代的通用闪存(UFS)集成到一个包中。这种内存是专门为下一代5G设备设计的。美光公司声称,与单独使用LPDDR5和UFS芯片的离散解决方案相比,uMCP5可以节省高达55%的PCB面积。

低功耗

在前一篇文章中,我们讨论了未来的5G系统将是非常复杂的,可能会使用带有数百个天线元件的大规模MIMO。有了这样耗电的系统,热管理是一个主要问题我们还需要将不同建筑模块的能耗降至最低。

新uMCP5的描绘。图片由微米

与微米级的LPDDR4解决方案相比,新产品中使用的LPDDR5内存减少了20%的功耗。与UFS 2.1产品相比,新设备提供了UFS 3.1,功耗减少了约40%。这些能效提升可以延长5G设备的电池寿命。

寿命、速度和存储空间

美光公司声称uMCP5NAND的续航能力提高了66%,可以延长未来智能手机的寿命。据美光公司介绍,其NAND内存可编程和擦除5000次,而不会降低设备性能。

与UFS 2.1产品相比,UFS 3.1的写速度提高了20%,顺序读操作的速度提高了两倍。这可以使下载速度提高20%,并促进5G能力。

与LPDDR4x产品相比,新产品中采用的LPDDR5技术将DRAM带宽提高了50%,达到约6,400 Mb/s。这使得数据密集型应用程序的多任务处理成为可能,并为高质量图像处理、虚拟现实、沉浸式游戏和边缘计算等数据丰富的特性铺平了道路。