行业白皮书

使用集成宽带DAC和ADC中的多芯片同步功能的加电相确定性

白皮书概述

在单个整体芯片中的多个数字信号处理(DSP)块,宽带数字到Analog转换器(DAC)和宽带模数转换器(ADC)的集成使FPGA资源的卸载。这允许具有较小的占地面积,较低的功率和增加的通道计数平台,这些平台可以比以前可实现的速度更高。

随着这种新功能,这些集成电路(ICS)中的新颖的多芯片同步(MCS)算法,允许用户在为系统供电或对系统进行软件修改时实现所有通道的已知(确定性)阶段。这个确定性阶段简化了实现输出或输入到附加到这些ICS的前端网络处的所有通道所需的更广泛的系统级校准算法。

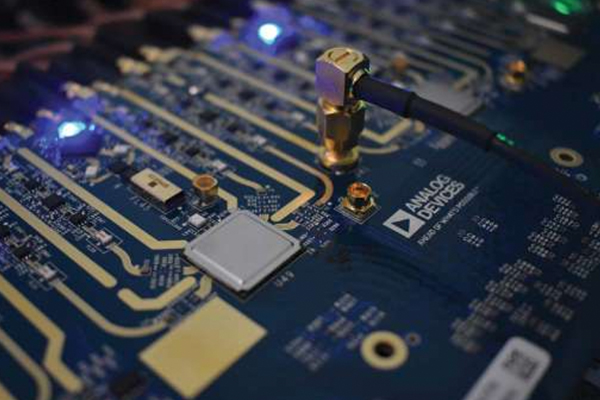

在本文中,您将看到结果可以证明MCS算法的功能,同时使用由多个数字化器ICS,时钟源和数字接口组成的16通道接收器/发射器平台。

错误