RISC-V:打开一个新时代的创新为嵌入式设计

2018年6月27日通过Ted Marena Microsemi本文还探讨了福利RISC-beplay体育下载不了V背后的开源硬件模型,讨论它的寿命,可移植性和可靠性。

本文还探讨了福利RISC-beplay体育下载不了V背后的开源硬件模型,讨论它的寿命,可移植性和可靠性。

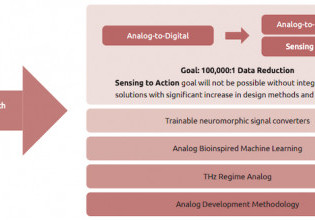

RISC-V为嵌入式应用程序背后的动力是不可否认的。RISC-V基金会今天,有超过100家公司背后的自由和开放RISC-V指令集架构(ISA)及其成员快速增长,随着越来越多的工具,软件,硬件和操作系统供应商。扩大生态系统、软硬件RISC-V给设计师一个令人信服的替代现任嵌入式处理器,处理器中引发了一个新时代的创新随着采用嵌入式设计。

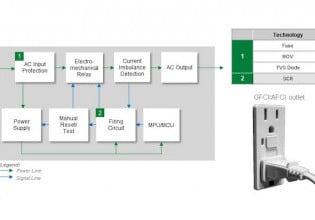

图1所示。RISC-V基金会营销的椅子上,Ted Marena礼物RISC-V的好处。

原因RISC-V开启一个新时代归结为三个关键因素:长寿,可移植性和可靠性。所有三个原因与让RISC-V尤其引人注目。与已经建立的处理器架构,通常添加指令,每一代,设计师可以依赖于一个固定的ISA RISC-V,确保他们的软件投资的长寿。这个长寿尤其有利于嵌入式应用程序功能安全,认证,和长时间的产品生命周期是很重要的。

冰冻的ISA

使RISC-V的广泛使用,让市场决定处理器架构,加州大学伯克利分校工程团队背后RISC-V冻结了ISA前不久他们25日热芯片介绍了技术研讨会于2014年。与非营利RISC-V基金会于2015年成立,成员的任务是指导未来发展HW / SW规范和生态系统,以及采用ISA开车。与基础ISA一成不变的可用和可选的扩展,设计师可以实现处理器根据他们特定的工作负载,而不是必须解决一个标准,现成的处理器设计,定制的余地很小。

现在支持RISC-V众多RTOS和完整的操作系统。嵌入式应用程序的RISC-V尤其有吸引力,因为越来越多的使用Linux操作系统。这使设计师能够迅速采用ISA作为一个新的开放标准架构直接本地硬件实现。Linux不被使用,然而,即使冻架构,长寿,可移植性和可靠性,ISA有助于是关键因素需要考虑。

RISC-V扩展

冰冻的ISA意味着软件可以无限期地一次性开发和运行在任何RISC-V设备,支持扩展(如果有的话)。扩展是唯一的方法可以添加新的指令。目前,有5个扩展,这也被冻结。这些扩展包括:

- 美元整数乘法和除法。

- 一个原子指令

- F为单精度浮点

- D为双精度浮点

- C压缩指令

RISC-V处理器的好处

这种程度的可预测性和简单处理器的设计和软件开发有很多好处。让我们来看看每一个接一个。

长寿

RISC-V ISA提供一个稳定、层次清晰的设计平台和清晰的和用户之间的安全隔离和特权模式因为ISA是固定的,包含小于50指令。如果所有的多个标准扩展实现,总数还不到200。而不是介绍ISA的新版本,添加到标准指令集是通过扩展,促进未来设计额外的稳定性。更少的指令意味着可以创建简单的架构,导致成本效益和估计在处理器实现。对于软件开发人员来说,这意味着保护投资。编写软件,运行它永远对任何RISC-V核心。这通常是关键的产品必须支持产品寿命长,几十年来,以及应用程序必须遵守严格的认证要求,软件不能修改。

可移植性

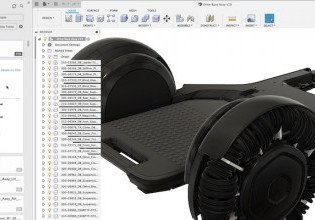

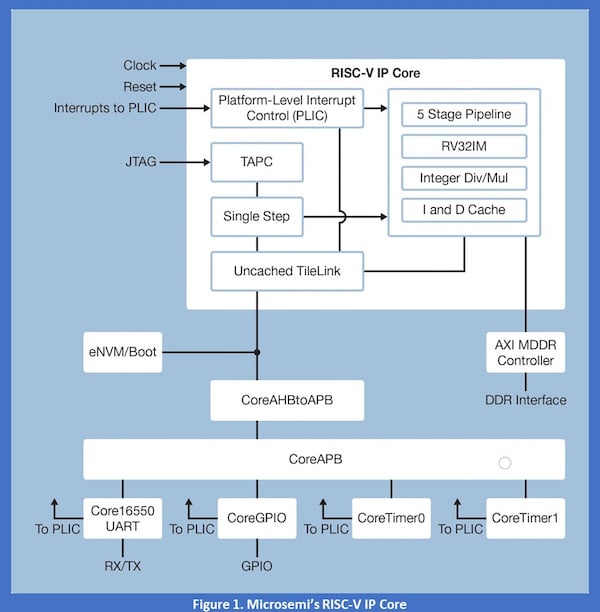

RISC-V更便于设计高容量增加。例如,一个设计可以开始航运软RISC-V运行的FPGA核心(图1)。因为软件将完全移植到任何RISC-V核心设备,设计师有什么本质上是一种“免版税”处理器子系统RTL代码可以在硬件中实现的。设计师可以修改、调整和迁移他们的设计为他们的产品的最佳平台。如果选择FPGA需要替换为新一代设备,不需要重写软件代码。现有的源RTL只需要gdp8 % FPGA。另外,如果数量达到足够高的水平,同样的RTL源代码可以gdp8 %的ASIC,无需支付任何版权使用费。这种情况是不可能的用一只胳膊或x86处理器类型。

图2。RISC-V IP核心图表。

可靠性和安全性

RISC-V的灵活性使独特的解决方案,特别是为嵌入式设计要求功能安全。例如,在多个系统中,功能与核心自主设计的终极冗余。其中一个核心可能是Microsemi Mi-V RV32IM,和其他核心功能上等价,但是完全不同,内部设计。RISC-V还允许完整的灵活性在微体系结构;一个核心可以提供单独的事件打乱(SEU)为数据和指令缓存内存的保护措施。可以使用许多其他安全防范技术因为RISC-V允许访问RTL。

虽然英特尔x86和ARM处理器架构的完善的变化不太可能很快消失,RISC-V处理器在嵌入式市场生态系统正在经历快速发展阶段给予的自由设计师必须定制。处理器体系结构的设计本质上是灵活的,这样一个实现可以有一些业务在硬件加速,或者,例如,专为低功耗优化。设计师也有附加任何他们所希望的总线接口的灵活性,而不是与处理器建立供应商提供的公共汽车。由于ISA的固定性质,任何变化RISC-V微体系结构是可以接受的。

RISC-V资源

更多地了解RISC-V为您的下一个设计,有几个地方开始。

关于RISC-V及其成员的背景信息,访问RISC-V基金会网站。如果你想闪的,开始C编码为一个RISC-V核心,去Microsemi Github网站和检查IGLOO2创意开发板RISC-V项目。Microsemi是第一个FPGA供应商提供一个开放的体系结构软件IDE RISC-V IP核心和一个全面的解决方案。设计师可以部署在多个基于flash的fpga RISC-V IP核,包括PolarFire fpga, IGLOO2和RTG4设备。Mi-V创意板(图2)包含一个IGLOO2 FPGA与RISC-V预排程序的核心,“hello world”的盒子。

软件代码开发,基于eclipse的软控制台集成开发环境(IDE)驻留在Linux或Windows平台提供了完整的开发支持,包括C或c++编译器和调试器功能。的Microsemi RISC-V IP核心,自由人SoC发展软件和软控制台IDE都可以下载免费的Microsemi Github的网站。

图3。M2GL025创意与预排程序的RISC-V核心

冷冻ISA、简单、可移植性和可靠性、RISC-V给设计师一个全新的处理器范式的超越的约束建立了处理器的现状,推动创新的边界。

文章内容的一种形式,允许行业合作伙伴分享有用的新闻,信息,技术和关于电路的读者的方式编辑内容并不适合。所有行业的文章受到严格的编辑指南的目的是提供读者有用的消息,技术专长,或故事。在行业的文章中表达的观点和意见不一定是合作伙伴和所有的电路或其作家。